#### Module 1

NETHRAVATHI H M Assistant Professor BGSIT,ACU

#### **Optoelectronic Devices**

- Study of devices that emit, detect and control light in the wavelength spectrum ranging from ultraviolet to far infrared

- Includes

- Electrical-to-optical transducers

- Optical-to-electrical transducers

#### Photodiode

- Light detector semiconductor device that converts light energy into electric current or voltage which depends upon the mode of operation

- Upper cut-off wavelength  $\lambda = 1240/E_0$

- (Fg bandgap energy)

#### p-n junction diode

- Under reverse bias, a small amount of electric current generated due to minority charge carriers

- Application of external reverse voltage to the p-n junction diode will not increase the population of minority charge carriers

- Reason: Minority carriers generated at n-side or p-side will recombine in the same material, before they cross the junction

- No electric current flows.

#### Photodiode

- Apply external energy directly to the depletion region to generate more charge carriers

- Photodiode is designed to generate more number of charge carriers in depletion region

- Light or photons as the external energy to generate charge carriers in depletion region

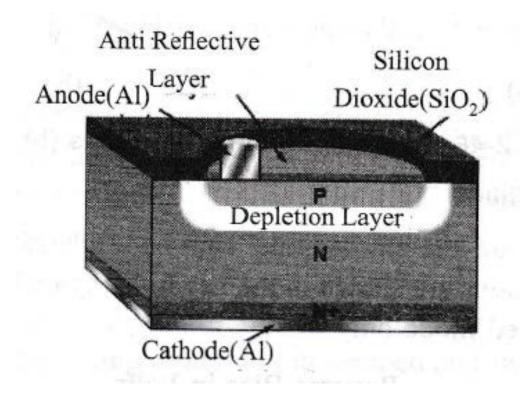

#### Photodiode: Construction

- ion implantation: surface of a layer of N-type is bombarded with P- type silicon ions to produce a P-type layer

- Diffusion: excess electrons move from N-type towards P-type and excess holes move from Ptype towards N-type

- Results in the removal of free charge carriers close to the PN-junction, so creating a depletion layer

#### Photodiode: Construction

#### Photodiode: Construction

- Silicon Dioxide (SiO2) in which there is a window for light to shine on the semiconductor.

- Silicon Nitride (SiN) to allow maximum absorption of light

- An anode connection of aluminium (AI) is provided to the P-type layer

- A more heavily doped N+ layer to provide a low resistance connection to the cathode

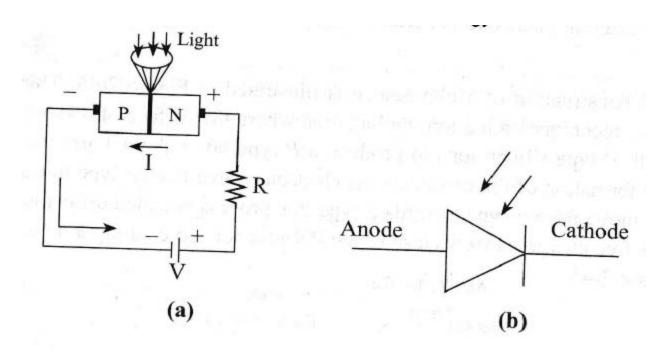

## Photodiode: Working Principle

- The junction of Photodiode is illuminated by the light source; the photons strike the junction surface.

- The photons impart their energy in the form of light to the junction.

- Due to which electrons from valence band get the energy to jump into the conduction band.

- This leaves positively charged holes in the valence band, so producing 'electron-hole pairs' in the depletion layer.

### Photodiode: Working Principle

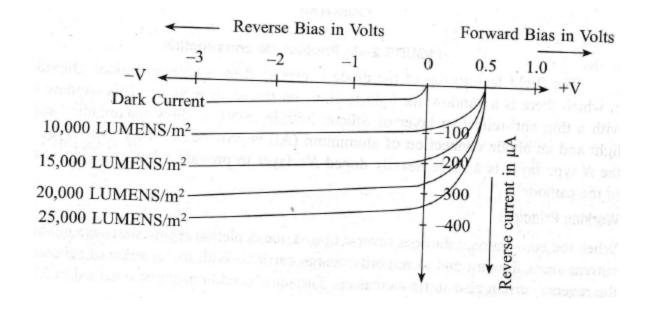

#### Photodiode: V-I Characteristics

Reverse bias current is the summation of reverse saturation current and short circuit current.

### Photodiode: Applications

- Consumer electronics devices like smoke detectors, compact disc players, and televisions and remote controls in VCRs.

- Photodiodes are frequently used for exact measurement of the intensity of light in science and industry.

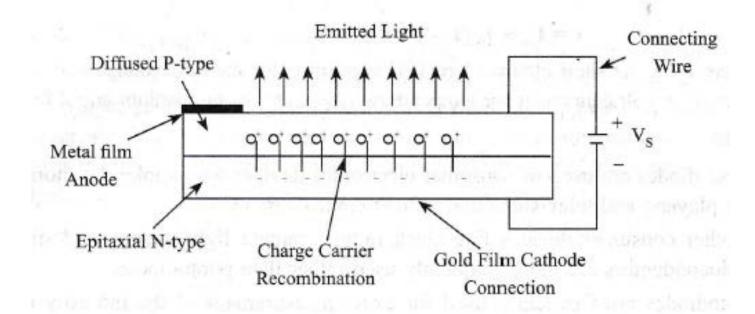

## Light Emitting Diode (LED)

- The LED is a PN-junction diode which emits light when an electric current passes through it in the forward direction

- Electroluminescence is the properly of the material to convert electrical energy into light energy

- The semiconductor material used in LED is Galliurn Arsenide (GaAs), Gallium phosphide (GaP) or Gallium Arsenide Phosphide (GaAsP).

- The semiconductor layer of P-type is placed above N-type because the charge carrier recombination occurs in P-type.

- If P-type is placed below the N-type, the emitted light cannot be seen.

- The semiconductor material used in LED is Galliurn Arsenide (GaAs), Gallium phosphide (GaP) or Gallium Arsenide Phosphide (GaAsP).

- The semiconductor layer of P-type is placed above N-type because the charge carrier recombination occurs in P-type.

- The P-type layer is formed from diffusion of semiconductor material.

- The metal film is used on the P-type layer to provide anode connection to the diode.

- Gold-film layer is coated on N-type to provide cathode connection. The Gold-film layer on N-type also provides reflection from the bottom surface of the diode.

- If any significant part of radiated light tends to hit bottom surface then that will be reflected from the bottom surface to the device top surface. This increases LED's efficiency.

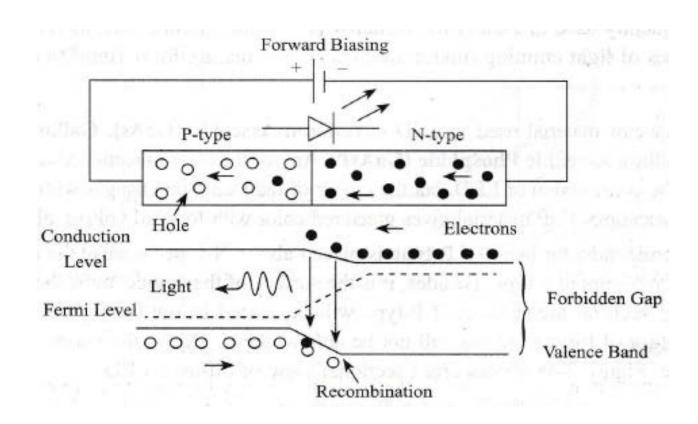

## LED: Working Principle

- The charge carriers recombine in a forward-biased P-N junction as the electrons cross from the Nregion and recombine with the holes existing in the P-region.

- Free electrons are in the conduction band of energy levels

- Holes are in the valence energy band.

- Energy level of the holes is less than the energy levels of the electrons.

- Some portion of the energy must be dissipated to recombine the electrons and the holes. This energy is emitted in the form of heat and light.

## LED: Working Principle

## LED: Working Principle

- Electron emit electromagnetic energy in the form of photons.

- The energy of photons is equal to the gap between the valence and the conduction band.

- Color of light can be determined by the band gap of semiconductor material.

#### LED: Applications

- LEDs are used in remote control systems such TV or LCD remote.

- Used in traffic signals for controlling the traffic crowds in cites.

- Used in digital computers for displaying the computer data.

- Used in electronic calculators for showing the digital data.

- Used in digital watches and automotive heat lamps.

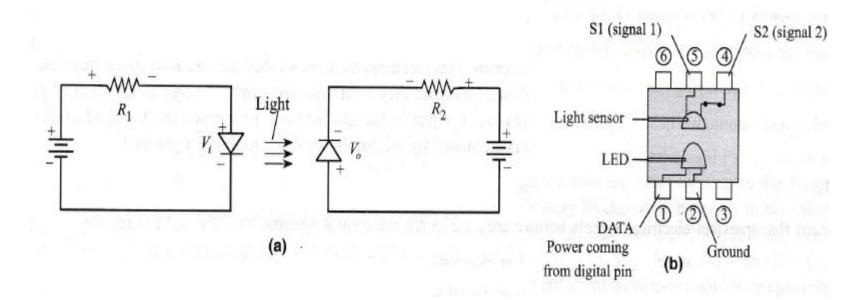

#### Photocoupler

Photocoupler or Optocoupler is a device that transfers electrical signals between two isolated circuits by using light.

### Photocoupler: Construction

All optocouplers consist of two elements: a light source (a LED) and a photosensor (a photoresistor, photodiode, phototransistor, silicon-controlled rectifier (SCR), or triac); which are separated by a dielectric (non-conducting) barrier

## Photocoupler: Working

- When input current is applied to the LED, it switches ON and emits infrared light

- The photosensor then detects this light and allows current to flow through the output side of the circuit

- When the LED is off, no current will flow through the photosensor.

- By this method, the two flowing currents are electrically isolated. It consists of LED and photodiode; where the circuits are isolated electrically.

- In the following Figure, LED is forward biased, photodiode is reverse biased and output exists across R2.

## Photocoupler: Working

### Photocoupler: Applications

- Input and output switching in electronically noisy environments.

- Controlling transistors and triacs.

- Switch-mode power supplies.

- PC/ Modem communication.

- Signal isolation.

- Power control.

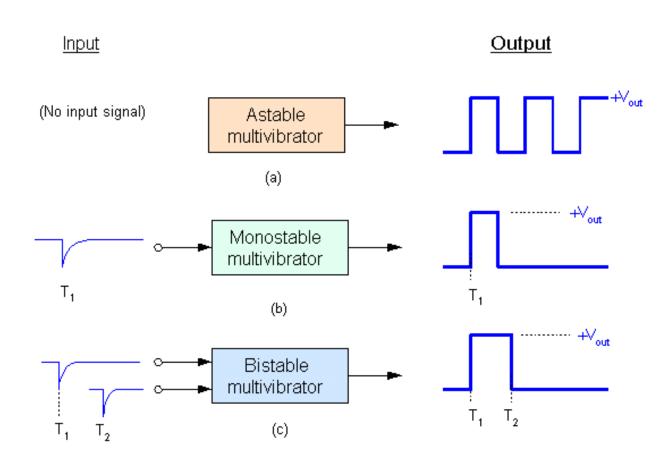

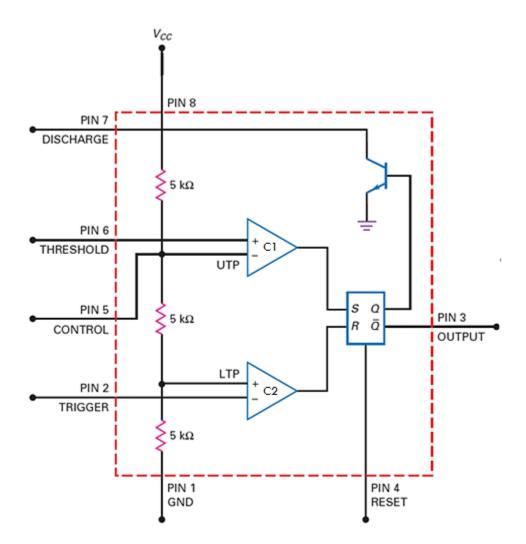

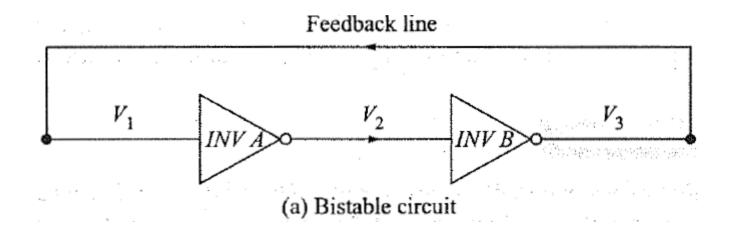

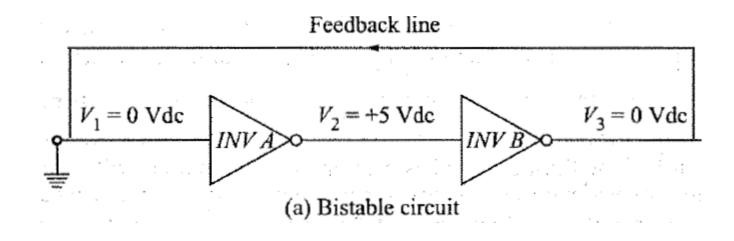

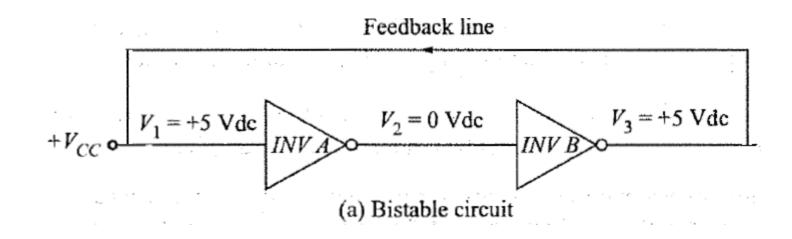

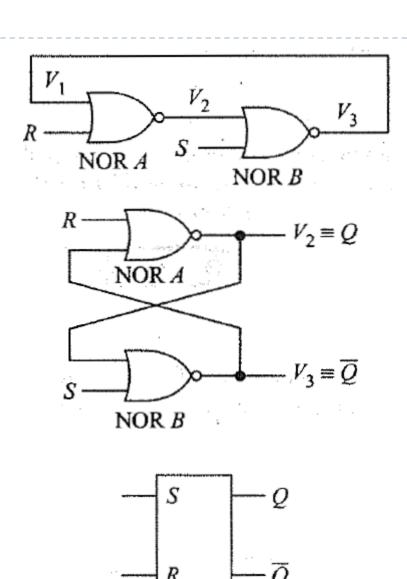

#### MULTIVIBRATORS USING IC-555

- A multivibrator circuit oscillates between a "HIGH" state and a "LOW" state producing a continuous output.

- It generates square, rectangular, pulse waveforms, also called nonlinear oscillators or function generators.

- There are basically three types of clock pulse generation circuits:

- Astable A free-running multivibrator that has NO stable states but switches continuously between two states this action produces a train of square/rectangular wave pulses at a fixed frequency.

- Monostable A one-shot multivibrator that has only ONE stable state and is triggered externally with it returning back to its first stable state.

- Bistable A flip-flop that has TWO stable states that produces a single pulse either positive or negative in

#### MULTIVIBRATORS USING IC-555

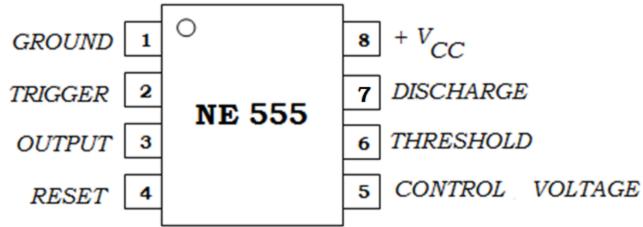

## Integrated Circuit(IC) Multivibrators

The NE555 (also LM555, CA555) is a widely used IC timer, a circuit that can run in either of two modes: monostable (one stable state) or astable (no stable states)

## Integrated Circuit(IC) Multivibrators

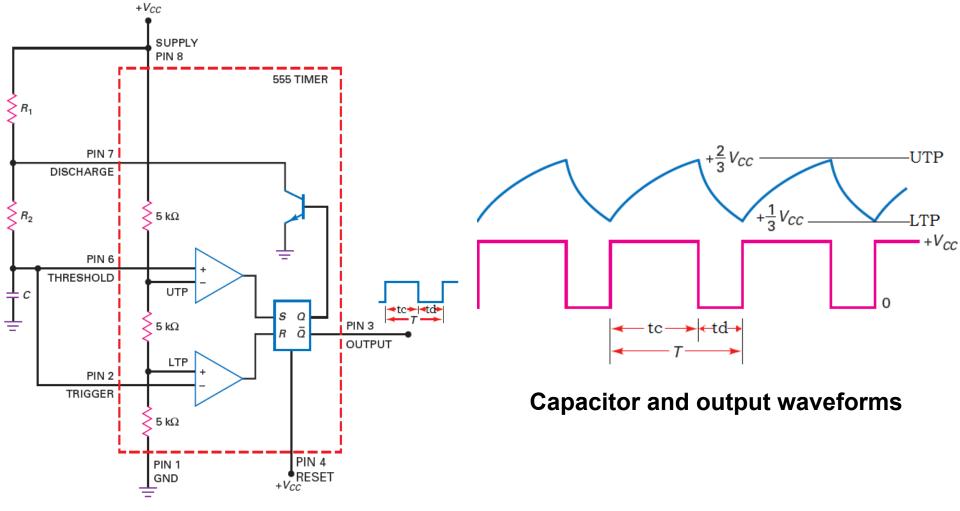

## Integrated Circuit(IC) Multivibrators Astable Operation of the 555 Timer

Circuit Diagram

Charge time (High Time)

$$t_c = 0.693(R_1 + R_2)C$$

Discharge time (Low Time)

$$t_d = 0.693R_2C$$

Total Time period T is

$$T = t_c + td$$

The frequency is given by

$$f_0 = \frac{1}{T}$$

· The duty cycle is

$$\square \%D = \frac{t_c}{T}$$

## Integrated Circuit(IC) Multivibrators Astable Operation of the 555 Timer

# Integrated Circuit(IC) Multivibrators Astable Operation of the 555 Timer

- When Q is low, the transistor is cut off and the capacitor is charging through R1 and R2 resistance. Because of this, the charging time constant is (R1+R2)C. As the capacitor charges, the threshold voltage (pin 6) increases. Eventually, the threshold voltage exceeds  $\frac{2}{3}V_{CC}$ . Then, the upper comparator sets the flip-flop.

- With Q high, the transistor saturates and grounds pin 7. The capacitor now discharges through R2. Therefore, the discharging time constant is R2C. When the capacitor voltage drops to slightly less than  $\frac{1}{3}V_{CC}$ , the lower comparator resets the flip-flop.

- The output is a rectangular wave that swings between 0 and V<sub>CC</sub>. Since the charging time constant is longer than the discharging time constant, the output is nonsymmetrical. Depending on resistances R1 and R2, the duty cycle is between 50 and 100 percent.

- □ When R1 is much smaller than R2, the duty cycle approaches 50 percent. Conversely, when R1 is much greater than R2, the duty cycle approaches 100 percent.

- To make the duty cycle to become less than 50 percent. By placing a diode in parallel with R2 (anode connected to pin 7), the capacitor will effectively charge through R1 and the diode. The capacitor will discharge through R2.

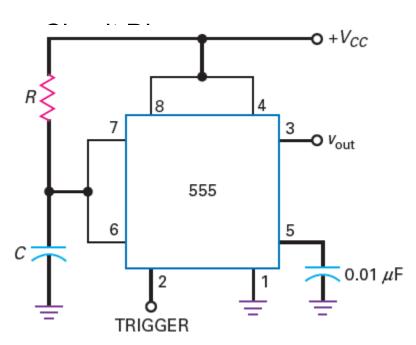

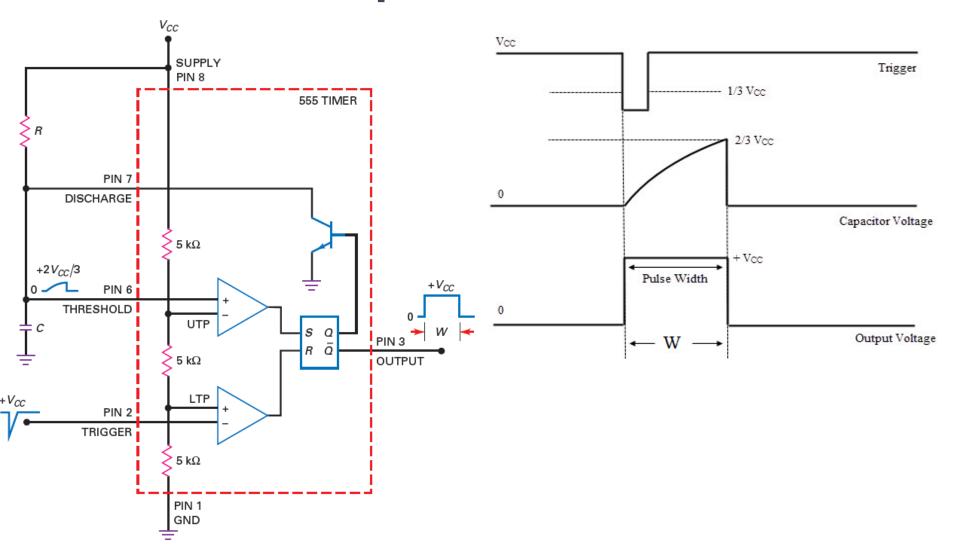

## Integrated Circuit(IC) Multivibrators Monostable Operation of the 555 Timer

- Pulse Width is

- W=1.1RC

- The circuit has an external resistor R and a capacitor C.

- The voltage across the capacitor is used for the threshold voltage to pin 6.

- When the trigger arrives at pin 2, the circuit produces a rectangular output pulse from pin 3.

# Integrated Circuit(IC) Multivibrators Monostable Operation of the 555 Timer

## Integrated Circuit(IC) Multivibrators Monostable Operation of the 555 Timer

- Initially, the Q output of the RS flip-flop is high. This turn ON the transistor and the capacitor discharge to ground through pin 7. The circuit will remain in this state until a trigger arrives at pin 2.

- When the trigger input falls to slightly less than  $\frac{1}{3}V_{CC}$  the lower comparator resets the flip-flop. Since Q has changed to low, the transistor goes OFF, allowing the capacitor to charge. At this time,  $\bar{Q}$  has changed to high.

- The capacitor now charges exponentially through R as shown in waveform. When the capacitor voltage is slightly greater than  $\frac{2}{3}V_{CC}$ , the upper comparator sets the flip-flop. The high Q turns ON the transistor, which discharges the capacitor almost instantly. At the same instant,  $\bar{Q}$  returns to the low state and the output pulse ends.

- oxdot remains low until another input trigger arrives.

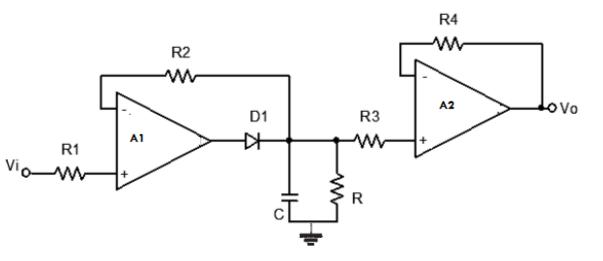

#### **Peak Detector Circuit**

<-T->

#### • RC ≥ 10 T

#### **Applications:**

- Used for AM in communication

- Used in test and measurement instrumentation applications.

## Peak Detector Circuit

- During +ve half cycle when the input voltage is positive, the diode is conducting/ON and capacitor charges to the peak of the input voltage.

- Second, when the input voltage is negative during –ve half cycle, the diode is non-conducting/OFF and the capacitor discharges through the load resistor.

- As long as the discharging time constant is much greater than the period of the input signal (T), the output voltage will be approximately equal to the peak value of the input voltage.

- This can achieved by making discharging time constant RC can be made much longer than the period of the input signal (RC ≥ 10 T), will get almost perfect peak detection of low-level signals.

- If the peak-detected signal has to drive a small load, to avoid loading effects by connecting the voltage follower (op-amp buffer) isolates the small load resistor from the peak detector. This prevents the small load resistor from discharging the capacitor too quickly.

## Comparator

- Comparator circuit compares a single voltage on one input of op-amp with a known voltage called reference voltage (Trip point or trigger point) on the other input and produces high or low output depending upon relative magnitude of two input.

- Comparators with Zero Reference

- Comparators with Nonzero References

- Comparators with Hysteresis or Schmitt Trigger

- Window Comparator

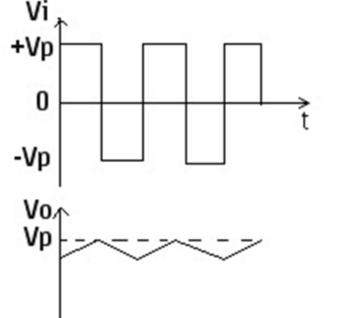

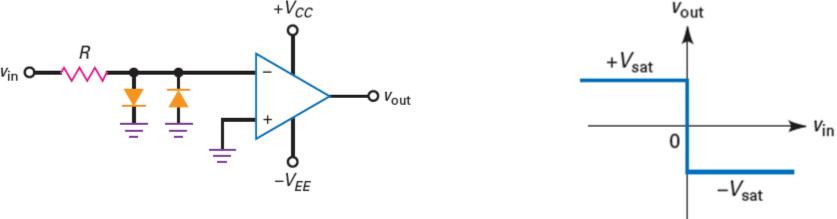

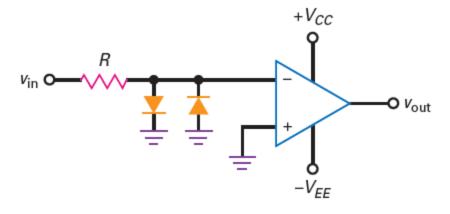

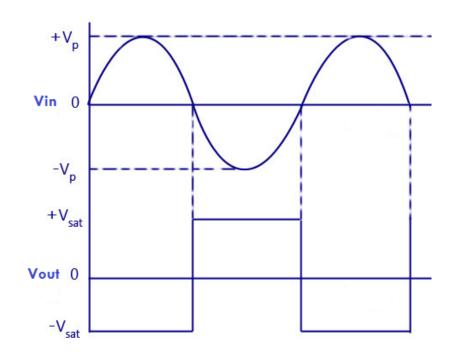

## Comparators with Zero Reference

Non-Inverting Comparator

- Because of the high open-loop voltage gain, a positive input voltage produces positive saturation, and a negative input voltage produces negative saturation.

- Above circuit is called a zero-crossing detector because the output voltage ideally switches from low to high or vice versa whenever the input voltage crosses zero (input compares with zero reference voltage).

## Comparators with Zero Reference

Non-Inverting Comparator

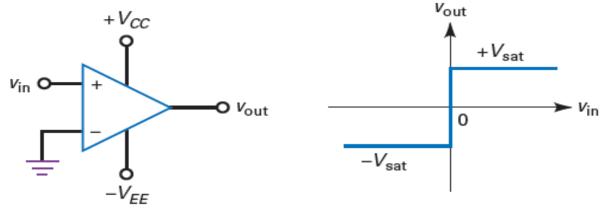

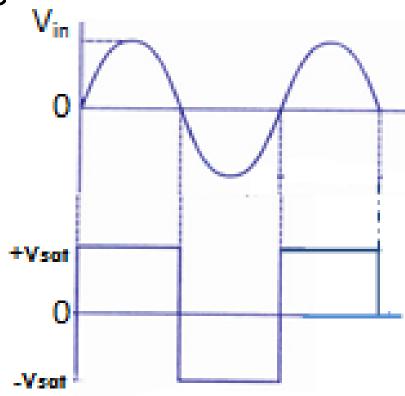

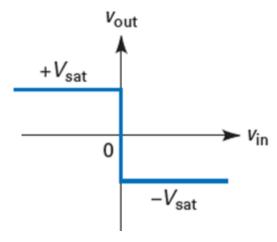

# Comparator With Zero Reference

The input signal drives the inverting input of the comparator. In this case, a positive input voltage produces a maximum negative saturation, as shown in above diagram. On the other hand, a negative input voltage produces a maximum positive saturation.

# Comparators with Zero Reference

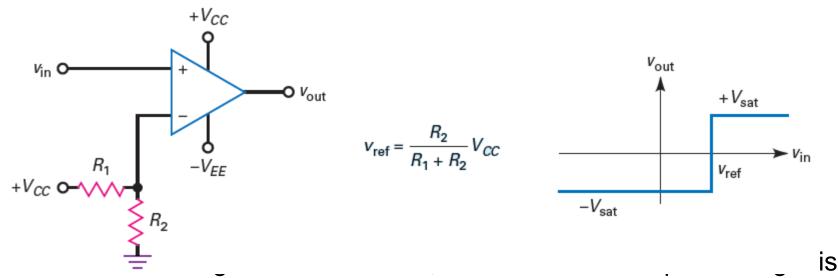

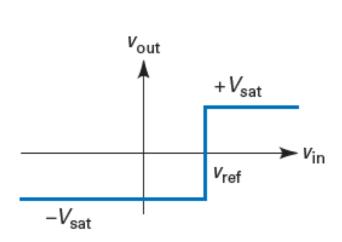

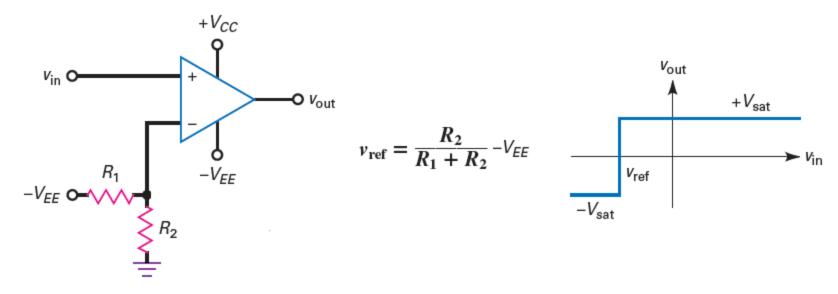

## Comparators with Nonzero

## References

Non-Inverting Comparator: Positive reference

positive and the output voltage is high (+Vsat). When Vin is less than Vref, the differential input voltage is negative and the output voltage is low (-Vsat).

- Vin > Vref then Vout = +Vsat

- Vin < Vref then Vout = Vsat</li>

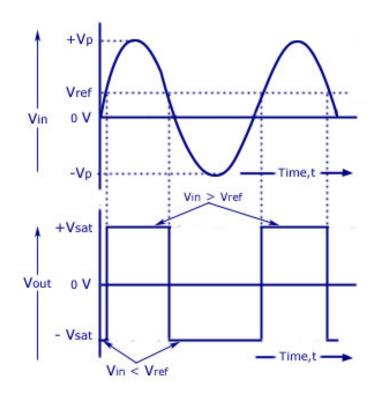

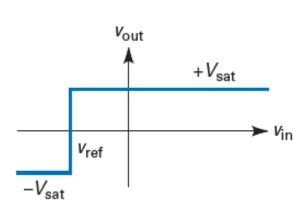

## Comparators with Nonzero References

Non-Inverting Comparator: Positive reference

Input and Output Waveforms For Positive Vref

## Comparators with Nonzero

## References

Non-Inverting Comparator: Negative reference

- Vin > Vref then Vout = + Vsat

- Vin < Vref then Vout = Vsat</li>

## Comparators with Nonzero References

Non-Inverting Comparator: Negative reference

Input and Output Waveforms For Negative Vref

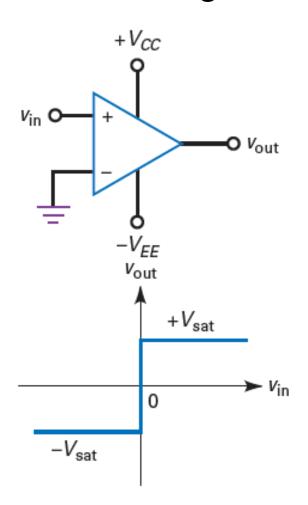

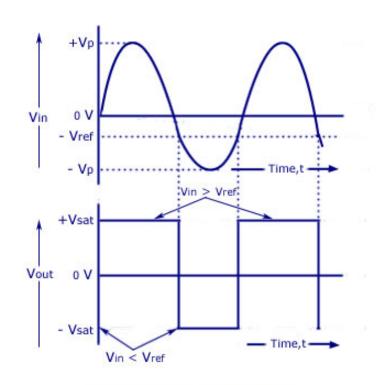

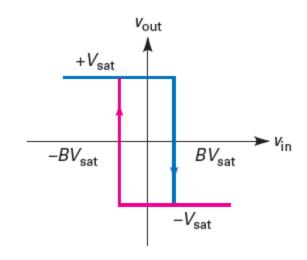

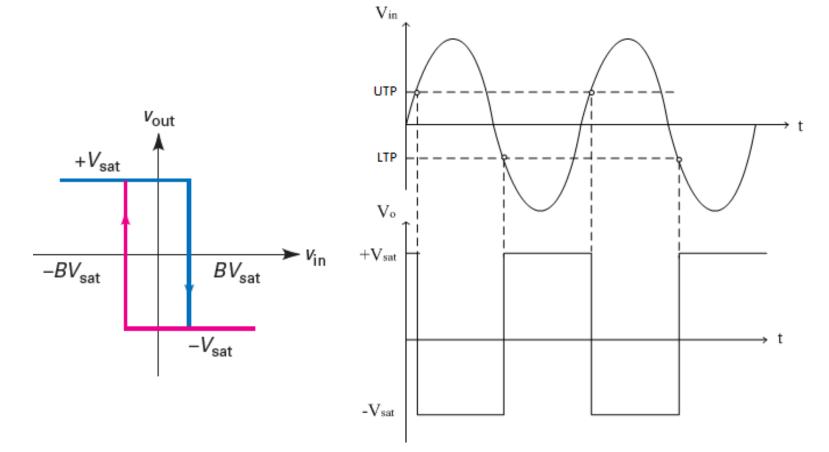

# Comparators with Hysteresis /Schmitt Trigger

- Inverting Schmitt trigger

- When the comparator is positively saturated, a positive voltage is fed back to the noninverting input. This positive feedback voltage holds the output in the high state.

- Similarly, when the output voltage is negatively saturated, a negative voltage is fed back to the noninverting input, holding the output in the low state.

$$B = \frac{R_1}{R_1 + R_2}$$

UTP =  $BV_{\text{sat}}$

LTP =  $-BV_{\text{sat}}$

$V_{\text{H}} = 2BV_{\text{sat}}$

Inverting Schmitt trigger

- Inverting Schmitt trigger

- The output voltage will remain in a given state until the input voltage exceeds the reference voltage for that state.

- For instance, if the output is positively saturated, the reference voltage is +BVsat. The input voltage must be increased to slightly more than +BVsat to switch the output voltage from positive to negative, as shown in input/output response has hysteresis.

- Once the output is in the negative state, it will remain there indefinitely until the input voltage becomes more negative than -BVsat. Then, the output switches from negative to positive shown in input/output response has

#### **Applications of Schmitt Trigger:**

Schmitt trigger is used in many applications, where level needs to be sensed. Hysteresis is used to reduce the multiple transitions that can occur around.

- Digital to analog conversion

- Level detection

- Line reception.

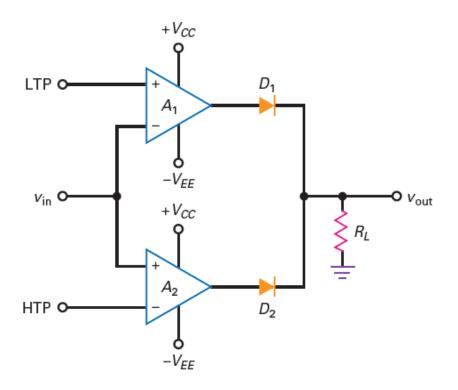

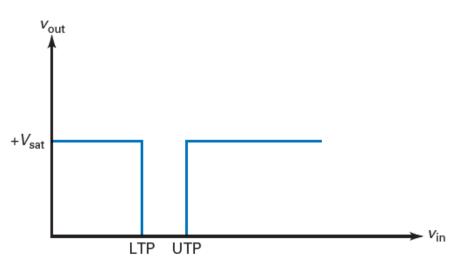

### Window Comparator

- An ordinary comparator indicates when the input voltage exceeds a certain limit or threshold.

- A window comparator (also called a doubleended limit detector) detects when the input voltage is between two limits called the window. To create a window comparator, will use two comparators with different thresholds.

## Window Comparator

#### Window Comparator

- Low Output between Limits

- Circuit shows a window comparator that can produce a low output voltage when the input voltage is between a lower and an upper limit.

- When Vin is less than LTP or greater than UTP, the output is high. When Vin is between LTP and UTP, the output is low.

- Operation:

- When Vin < LTP, comparator A1 has a positive output and A2 has a negative output. Diode D1 is on and D2 is off. Therefore, the output voltage is high.

- Similarly, when Vin > UTP, comparator A1 has a negative output and A2 has a positive output. Diode D1 is off, D2 is on, and the output voltage is high.

- When LTP < Vin < UTP, A1 has a negative output, A2 has a negative output, D1 is off, D2 is off, and the output voltage is low.

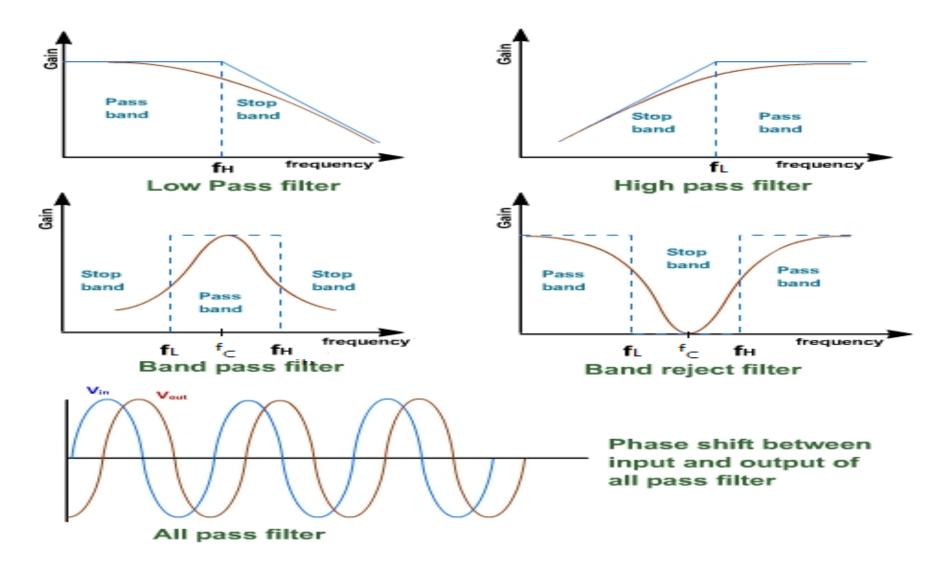

#### **Active Filters**

- An electric filter is often a frequency selective circuit that passes a specified band of frequency and blocks or attenuates signals of frequencies outside this band.

- Active filters employs transistor or op-amp in addition to resistor and capacitor.

- RC network are used for filter.

- The most commonly used filters are follows:

- Low pass filters

- High pass filter

- Band pass filter

- Band reject filter.

- All pass filter

- Next slide shows the frequency response characteristics of the five types of filter. The ideal response is shown by dashed line. While the solid lines indicates the practical filter response.

#### **Active Filters**

### **Active Filters**

- A filter that provides a constant output from dc up to a cut-off frequency f<sub>H</sub> and then passes no signal above that frequency is called an ideal low-pass filter.

- A filter that provides or passes signals above a cutoff frequency  $f_{\rm L}$  is a high-pass filter, as shown in previous slide.

- When the filter circuit passes signals that are above one ideal cutoff frequency (f<sub>L</sub>) and below a second cutoff frequency, (f<sub>H</sub>) it is called a bandpass filter.

- Two types of filters

- First Order Filter One capacitor used

- Second Order Filter Two or more capacitor used

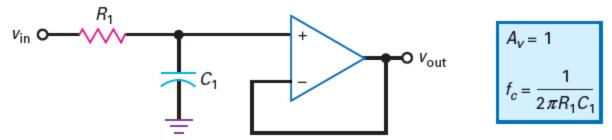

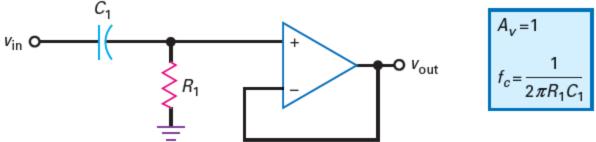

## Active Filters- Low-pass filter

#### Non-Inverting unity gain

- It is nothing more than an RC lag circuit and a voltage follower.

The voltage gain is: Av = 1.

- When the frequency increases above the cutoff frequency, the capacitive reactance decreases and reduces the noninverting input voltage.

- Since the R1C1 lag circuit is outside the feedback loop, the output voltage rolls off. As the frequency approaches infinity, the capacitor becomes a short and there is zero input voltage.

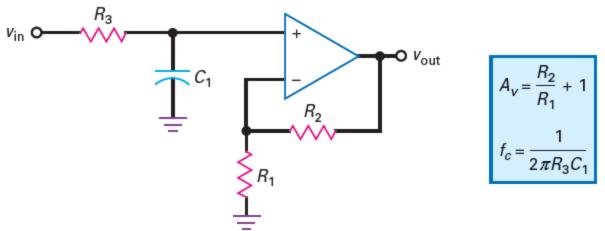

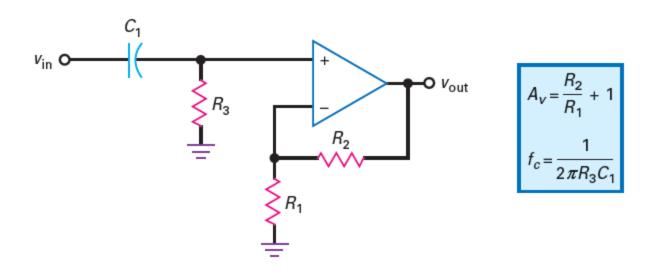

## Active Filters- Low-pass filter

Non-Inverting with voltage gain

Although it has two additional resistors, it has the advantage of voltage gain.

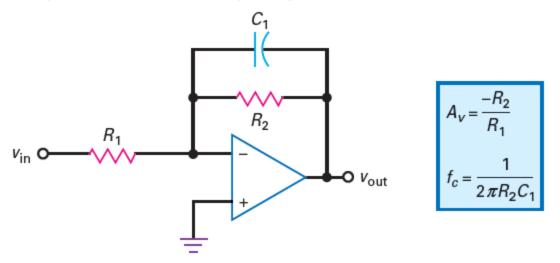

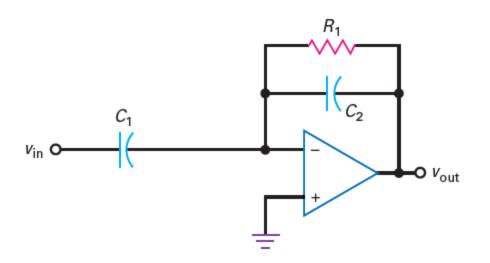

## Active Filters- Low-pass filter

Inverting with voltage gain

- As the frequency increases, the capacitive reactance decreases and reduces the impedance of the feedback branch. This implies less voltage gain.

- As the frequency approaches infinity, the capacitor becomes a short and there is no voltage gain.

## Active Filters- High-pass filter

Non inverting unity gain

- When the trequency decreases below the cutoff frequency, the capacitive reactance increases and reduces the noninverting input voltage.

- Since the R1C1 circuit is outside the feedback loop, the output voltage rolls off. As the frequency approaches zero, the capacitor becomes an open and there is zero input voltage.

## Active Filters- High-pass filter

Non-Inverting with voltage gain

## Active Filters- High-pass filter

Inverting with voltage gain

$$A_v = \frac{-C_1}{C_2}$$

$$f_c = \frac{1}{2\pi R_1 C_2}$$

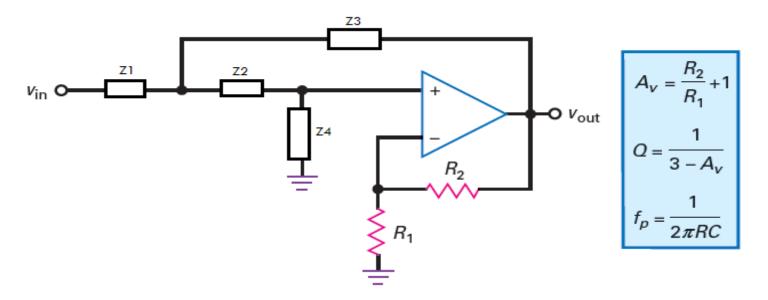

# Active Filters- Second Order Filter Low Pass/High Pass Filter

Generalized form of second order filter

- If Z1=Z2=R and Z3=Z4=C get second order low pass filter

- If Z1=Z2=C and Z3=Z4=R get second order high pass filter

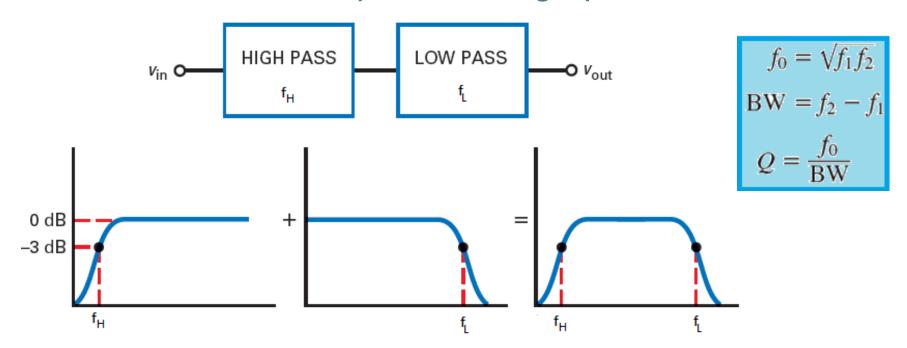

## Active Filters- Band-pass Filter

- Two types of band pass filter

- Wide band pass filter

- Narrow band pass filter

## Active Filters- Band-pass Filter

- Wide Band Pass Filters

- Cascade of low-pass and high-pass filter

## Active Filters- Band-pass Filter

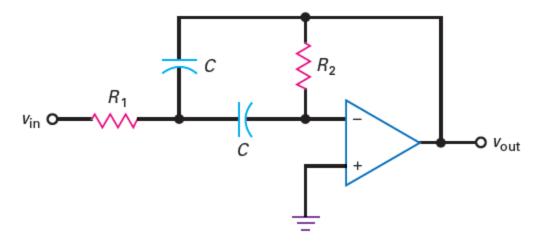

Narrow Band Pass Filters

$$A_{v} = \frac{-R_{2}}{2R_{1}}$$

$$Q = 0.5\sqrt{\frac{R_{2}}{R_{1}}}$$

$$f_{0} = \frac{1}{2\pi C\sqrt{R_{1}R_{2}}}$$

In the circuit the input signal goes to the inverting input rather than the noninverting input.

Also the circuit has two feedback paths, one through a capacitor and another through a resistor.

## Non-Linear Amplifier

- In this amplifier the gain value is non-linear function of the amplitude of the input signal.

- The gain may be large for weak signal and very small for large signal this can achieved using non-linear device such as PN junction diode as shown belo

# Non-Linear Amplifier

#### Working:

- For small value of input signal, diodes act as open circuit and the gain is high due to minimum feedback.

- When the amplitude of input signal is large, diodes offer very small resistance and thus gain is low.

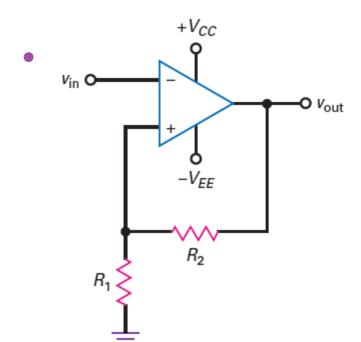

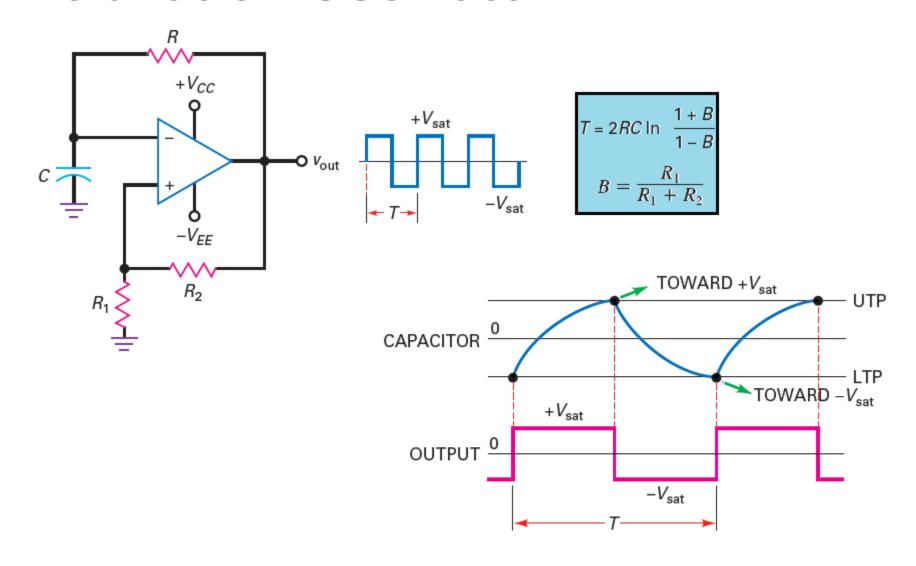

### **Relaxation Oscillator**

## **Relaxation Oscillator**

- In circuit, there is no input signal.

- Nevertheless, the circuit produces a rectangular output signal.

This output is a square wave that swings between –Vsat and +Vsat. How is this possible?

- Assume that the output is in positive saturation. Because of feedback resistor R, the capacitor will charge exponentially toward +Vsat, as shown in waveform. But the capacitor voltage never reaches +Vsat because the voltage crosses the UTP. When this happens, the output square wave switches to -Vsat.

- With the output now in negative saturation, the capacitor discharges, as shown in waveform. When the capacitor voltage crosses through zero, the capacitor starts charging negatively toward –Vsat. When the capacitor voltage crosses the LTP, the output square wave switches back to +Vsat. The cycle then repeats.

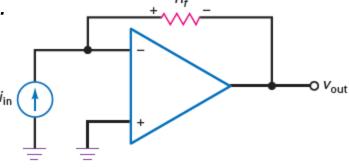

## **Current-To-Voltage Converter**

Also called transimpedance amplifier

Consider the simple Op-Amp circuit to convert I to V, as shown in

the following Figure.

Since, current through the Op-Amp is negligible;  $I_S = I_f$

$$I_s = I_f = \frac{V_B - V_0}{R_f}$$

By virtual ground concept; as node A is grounded, node B will be virtually grounded. Therefore,  $V_B = 0$ . Therefore,

$$I_s = \frac{-V_0}{R_f} \quad Or, \quad V_0 = I_S R$$

Thus, output is proportional to the input current  $I_S$ , and the circuit works as I to V converter.

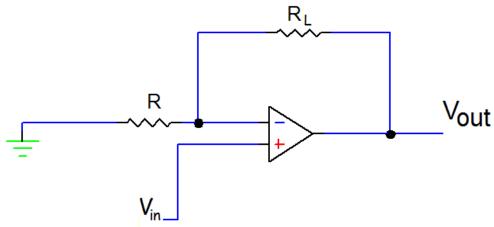

## **Voltage-To-Current Converter**

- Also called transconductance amplifier

- For a single input, the current in the load resistor is given by I<sub>L</sub> = I = Vin/R. from this equation it is obvious that the output current I<sub>L</sub> is independent of load resistance and is proportional to the input voltage. This is because of the virtual ground at the inverting input terminal of the opamp.

#### **VOLTAGE REGULATORS** Introduction

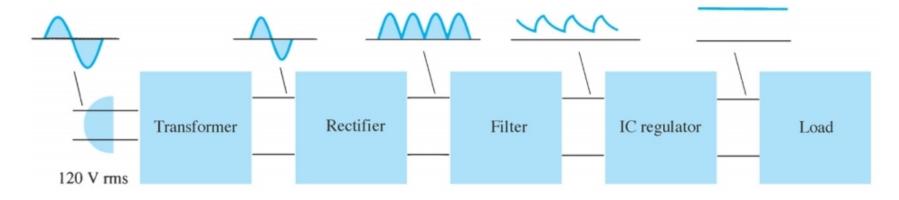

- Power supply: a group of circuits that convert the standard ac voltage (120 V, 60 Hz) provided by the wall outlet to constant dc voltage

- Transformer: a device that step up or step down the ac voltage provided by the wall outlet to a desired amplitude through the action of a magnetic field

•

#### **VOLTAGE REGULATORS** Introduction

- Rectifier: a diode circuits that converts the ac input voltage to a pulsating dc voltage

- The pulsating dc voltage is only suitable to be used as a battery charger, but not good enough to be used as a dc power supply in a radio, stereo system, computer and so on.

- Filter: a circuit used to reduce the fluctuation in the rectified output voltage or ripple. This provides a steadier dc voltage.

- Regulator: a circuit used to produces a constant do output voltage by reducing the ripple to negligible amount.

One part of power supply.

#### **VOLTAGE REGULATORS** Introduction

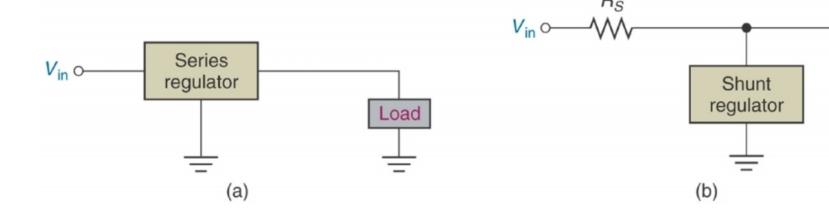

- Voltage regulation is the process of keeping a voltage steady under conditions of changing applied voltage, changing load and temperature.

- There are two types of voltage regulators: shunt and series.

#### **NEED FOR REGULATORS**

A voltage regulator is used for two reasons:-

- To regulate or vary the output voltage of the circuit.

- To keep the output voltage constant at the desired value inspite of variations in the supply voltage or in the load current.

# **VOLTAGE REGULATORS: Factors Affecting the Load Voltage:**

- Load current (I<sub>L</sub>): Ideally the output voltage should remain constant in-spite of changes in the load current, but practically the power supply without regulator, the load voltage decreases as load current, I<sub>L</sub>, increases. For practical power supply regulator, the load voltage must be constant through load to full load condition.

- Line voltage: The input to the rectifier is AC (230 V) is the line voltage. This input decides the

output voltage level. If input changes, output also changes. So this affects the performance of

power supply. So ideally voltage must remain constant irrespective of any changes in the line

voltage.

- Temperature: In the power supply, the rectifier unit is used which uses PN-junction diode. As the

diode characteristics are temperature dependent, the overall performance of the power supply is

temperature dependent.

# **VOLTAGE REGULATORS:**Performance Parameters of a Power Supply:

- 1. Line Regulation: If the input to the rectifier unit i.e. 230 V changes, the output DC of rectifier will also change and since the output of rectifier is applied to the regulator, the output of regulator will also vary. Thus the source causes the change in output. This is as source regulation or line regulation. It is defined as the change in regulated DC output for a given change in input (line) voltage. Ideally the source regulation should be zero and practically it should be as low as possible.

- 2. Load Regulation: Load regulation is defined as the change in the regulated output voltage when load current is changed from zero (no load) to maximum value (full load). The load regulation ideally should be zero, but practically it should be as small as possible. The following Figure shows the load regulation characteristics. Percentage load regulation =  $\left[\frac{V_{NL}-V_{FL}}{V_{FL}}\right]$  \* 100

# **VOLTAGE REGULATORS:**Performance Parameters of a Power Supply:

- 3. Voltage Stability factor (S<sub>V</sub>): Voltage stability factor shows the dependency of output voltage on the input line voltage. Voltage stability factor is defined as the percentage change in the output voltage which occurs per volt change in input voltage, where load current and temperature are assumed to be constant. Smaller the value of this factor, better is the performance of power supply.

- 4. Temperature Stability Factor (S<sub>r</sub>): As in the chain of power supply we are using semiconductor devices (diodes in rectifier block) the output voltage is temperature dependent. Thus the temperature stability of the power supply will be determined by temperature coefficients of various temperature sensitive semiconductor devices. So, it is better to choose the low temperature coefficient devices to keep output voltage constant and independent of temperature. S<sub>r</sub> must be as small as possible, and ideally it should it should be zero for a power supply.

- 5. Ripple Rejection Factor (RR): The output of rectifier and filter consists of ripples. Ripple rejection is defined as a factor which shows how effectively the regulator rejects the ripples and attenuates it from input to output. As ripples in the output are small compared to input, the RR is very small and in dB, it is in negative value. Ripple rejection factor = \frac{V\_{RIPPLE} (OUTPUT)}{V\_{RIPPLE} (INPUT)}

When expressed in decibels, ripple rejection equals  $20 \log \left[ \frac{V_{RIPPLE} \ (OUTPUT)}{V_{RIPPLE} \ (INPUT)} \right] dB$

$$Also, V_{RIPPLE}(output) = \frac{v_{RIPPLE}(INPUT)}{1 + Loop \ Gain}$$

Load

#### **VOLTAGE REGULATORS: Types of Regulator**

- The series regulator is connected in series with the load

- The shunt regulator is connected in parallel with the load.

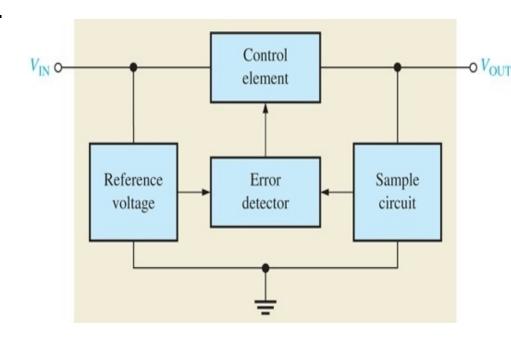

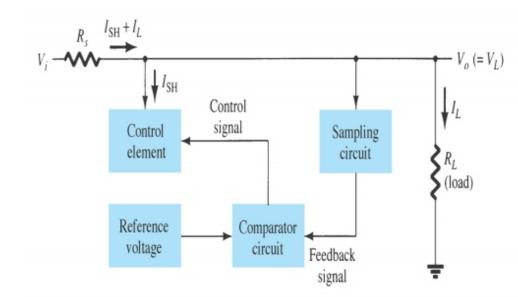

# **VOLTAGE REGULATORS: Series Regulator Circuit**

- Control element in series with load between input and output.

- Output sample circuit senses a change in output voltage.

- Error detector compares sample voltage with reference voltage → causes control element to compensate in order to maintain a constant output voltage

# **VOLTAGE REGULATORS: Series Regulator Circuit**

- The unregulated input voltage provides current to the load.

- Some of the current is pulled away by the control element.

- If the load voltage tries to change due to a change in the load resistance, the sampling circuit provides a feedback signal to a comparator.

- The resulting difference voltage then provides a control signal to vary the amount of the current shunted away from the load to maintain the regulated output voltage across the load.

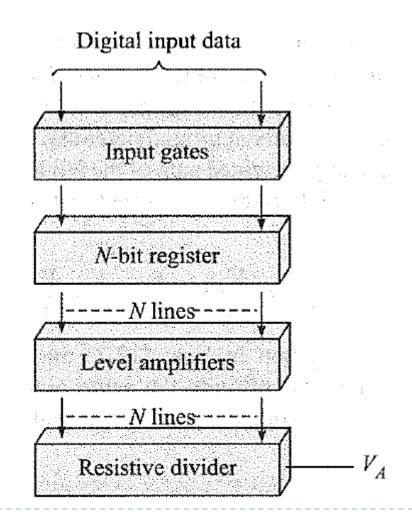

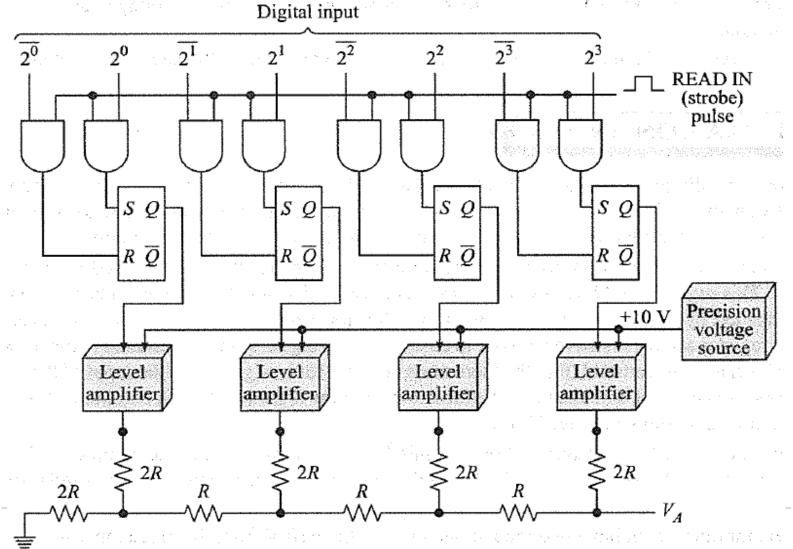

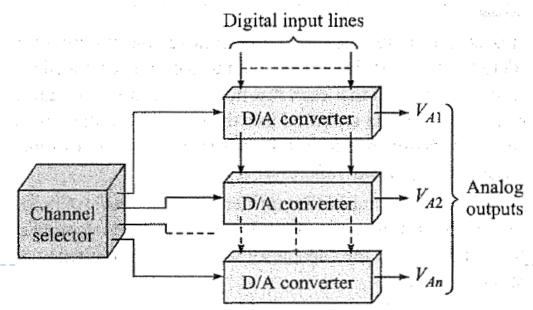

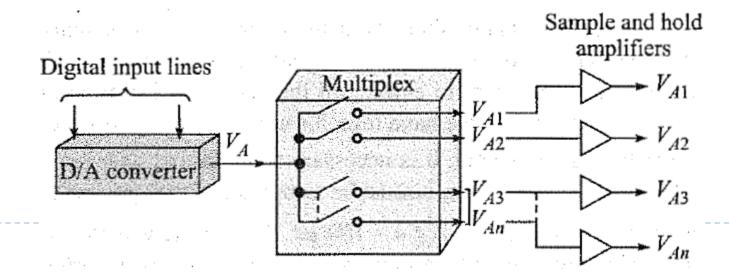

### D to A and A to D converter

- WHY A to D?

- Real world signal appear in analog form

- Difficult to process, transmit, store in physical form

- Computer perform operation quickly, efficiently

- Development in digital technology

- WHY D to A?

- Computer need to communicate with physical processes, people

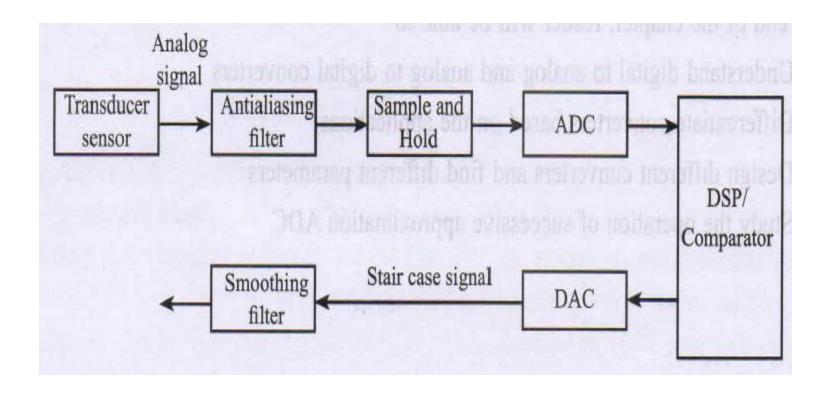

# Typical A/D and D/A Converter

# Typical A/D and D/A Converter

- Obtain analog signal from sensor or transducer

- Using anti aliasing filter restrict bandwidth of the signal

- Sample the signal at a frequency rate more than twice maximum frequency of band limited frequency

- 4. Hold sampled signal using hold circuit during conversion

# Typical A/D and D/A Converter

- 1. Feed the discrete signal to A to D Converter

- 2. A to D Converter converts the signal to digital signal

- Digital signal is converted to analog signal using D to A Converter

- 4. Output of D to A Converter is stair case waveform

- 5. Stair case waveform is passed through smoothing filter to remove quantized noise

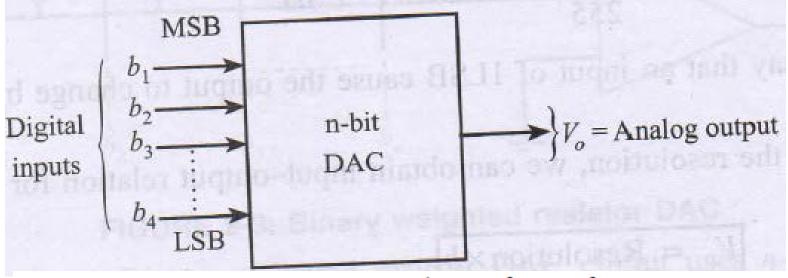

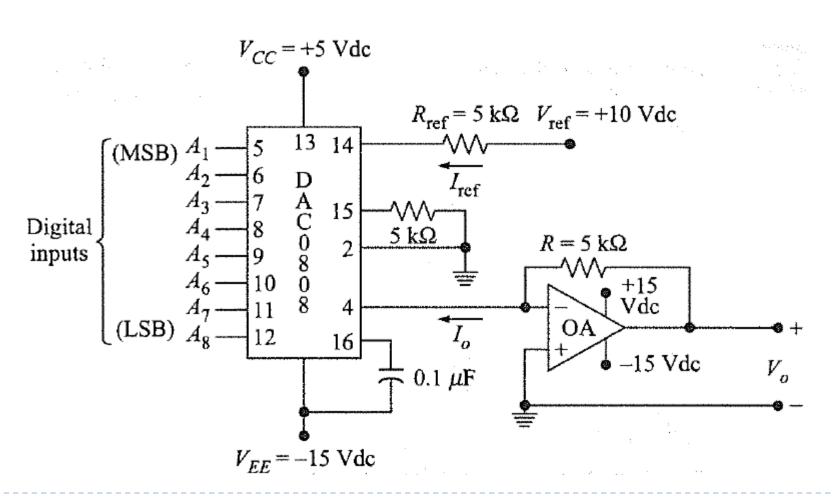

# Basic DAC Techniques

$$V_0 = kV_{FS}(b_1 2^{-1} + b_2 2^{-2} + b_3 2^{-3} + \dots b_n 2^{-n})$$

Where,  $V_0$  – Output voltage

$V_{FS}$  – Full scale output voltage

k – Scaling factor (usually 1)

$b_1$ ...,  $b_n$  – n-bit binary fractional word with decimal point located at the left

$b_1$  – MSB with a weight =  $V_{FS}/2$

$b_n$  – LSB with a weight =  $V_{FS}/2^n$

### Performance Parameters of DAC

#### 1. Resolution:

Ratio of change in output voltage resulting from a change of LSB at the digital input.

Resolution =

$$V_{OFS}/2^n - 1$$

$V_0$  = Resolution x b

#### 2. Accuracy

Measure of how close the actual output voltage is to the theoretical output value

$$Accuracy = \frac{V_{oFS}}{(2^n - 1)2}$$

### Performance Parameters of DAC

#### 3. Setting Time:

Setting time is the time required for a DAC output to settle within ± 1/2 LSB of final value for a given digital input.

#### 3. Stability:

The performance of a DAC is not stable due to the parameters such as temperature, power supply variations, and ageing.

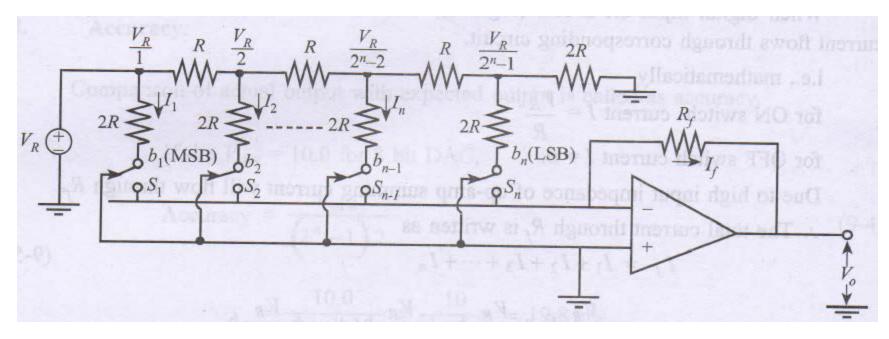

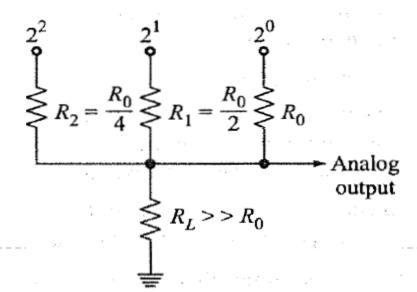

## Binary Weighted Resistor DAC

- When the switch is ON :  $I = V_R/R$

- When the switch is OFF: I = 0.

## Binary Weighted Resistor DAC

total current through R<sub>f</sub>

$$\begin{split} I &= I_1 + I_2 + I_3 + \dots + I_n \\ &= \frac{V_R}{2^1 R} b_1 + \frac{V_R}{2^2 R} b_2 + \frac{V_R}{2^3 R} b_3 + \dots + \frac{V_R}{2^n R} b_n \\ &= \frac{V_R}{R} [b_1 2^{-1} + b_2 2^{-2} + b_3 2^{-3} + \dots + b_n 2^{-n}] \end{split}$$

The output voltage is;  $V_0 = -I_f R_f$

$$i.e., V_0 = \frac{-V_R}{R} R_f [b_1 2^{-1} + b_2 2^{-2} + b_3 2^{-3} + \dots + b_n 2^{-n}]$$

If  $R_f = R$ ; Or,  $V_0 = -V_R [b_1 2^{-1} + b_2 2^{-2} + b_3 2^{-3} + \dots + b_n 2^{-n}]$

### Drawbacks of DAC

- Large range of resistor values are required, as resistance values increases like 2<sup>1</sup>R, 2<sup>2</sup>R, 2<sup>3</sup>R, . . . , 2<sup>n</sup>R.

- Practically it's difficult to fabricate large values of resistors on IC.

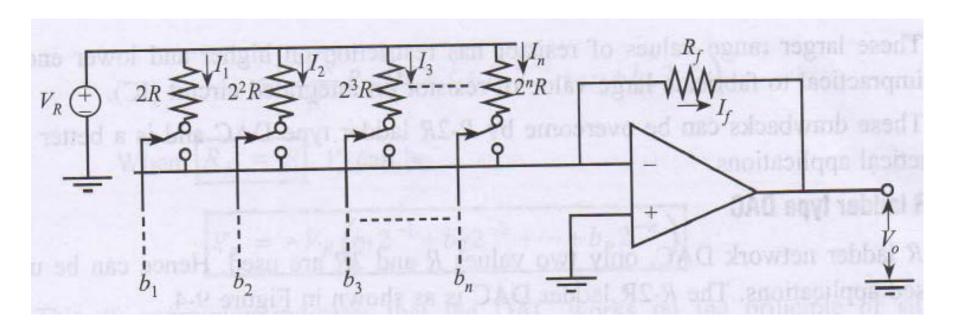

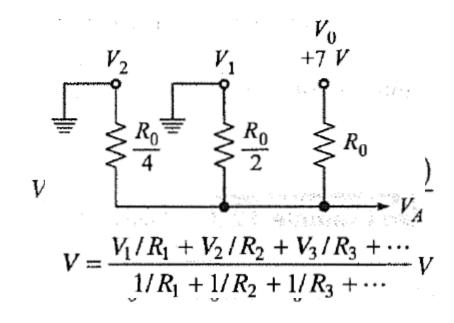

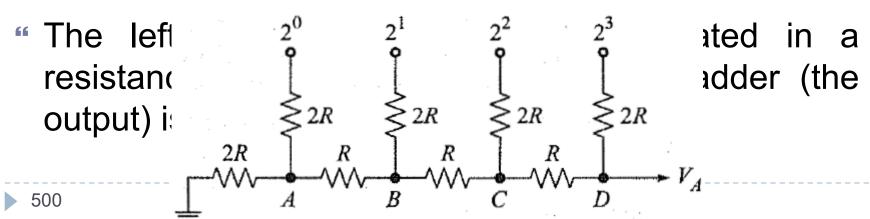

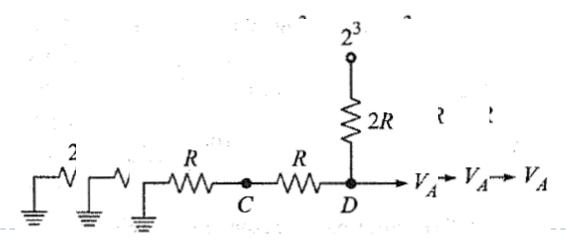

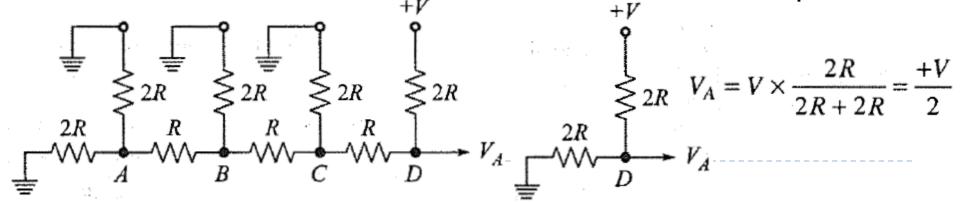

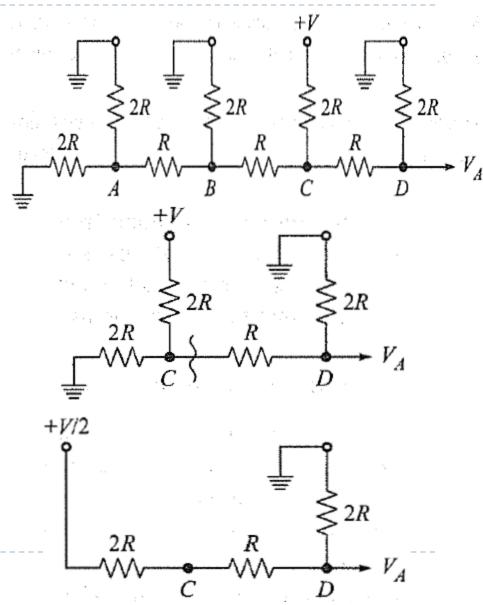

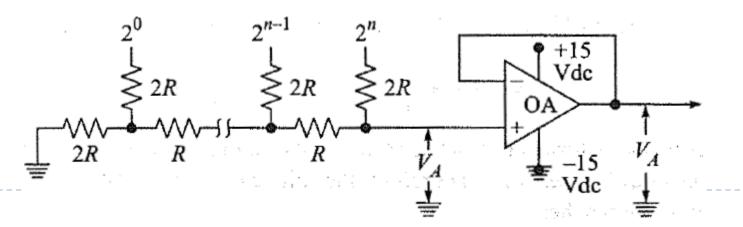

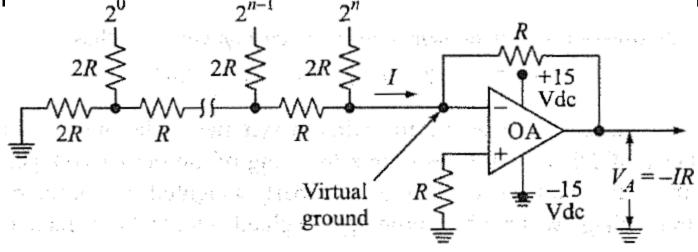

# R-2R Ladder type DAC

Due to virtual ground, both the positions of the switches are at ground potential, and currents through the resistances are constant.

# R-2R Ladder type DAC

The current flowing through each of 2R resistances;

$$I_{1} = \frac{V_{R}}{2R} \qquad I_{2} = \frac{V_{R}/2}{2R} = \frac{V_{R}}{4R} \qquad I_{3} = \frac{V_{R}/4}{2R} = \frac{V_{R}}{8R} \qquad I_{n} = \frac{V_{R}/(2^{n} - 1)}{2R}$$

$$\text{But, } V_{0} = -I_{f}R_{f} = -R_{f}(I_{1} + I_{2} + \dots + I_{N})$$

$$i.e., V_{0} = -R_{f}\left[\frac{V_{R}}{2R}b_{1} + \frac{V_{R}}{4R}b_{2} + \dots + \frac{V_{R}}{2^{n}R}b_{n}\right]$$

$$\text{Or, } V_{0} = -\frac{V_{R}}{R}R_{f}[b_{1}2^{-1} + b_{2}2^{-2} + \dots + b_{n}2^{-n}]$$

$$\text{If } R_{f} = R; \qquad V_{0} = -V_{R}[b_{1}2^{-1} + b_{2}2^{-2} + \dots + b_{n}2^{-n}]$$

# R-2R Ladder type DAC : Advantages

- As it requires only two types of resistors, fabrication and accurate value of R-@R can be designed.

- Node voltage remains constant, and hence, slow down effect can be avoided.

#### Example 1:

The digital input for a 4 bit DAC is D = 0111. Calculate its output voltage take  $V_{oFS} = 15 \text{ V}$ .

Resolution =

$$\frac{V_{oFS}}{2^n - 1} = \frac{15}{2^4 - 1} = 1 \text{ V/LSB}$$

$$\therefore V_o = \text{Resolution} \times D$$

$$D = Decimal values (0111) = 7$$

$$V_o = \frac{1 \text{ V}}{\text{LSB}} \times 7 = 7 \text{ V}$$

$$\therefore V_o = 7 \text{ V}$$

#### Example 2:

A 8 bit DAC having resolution of 22mv/LSB. Calculate V<sub>oFS</sub> and output if the input is (10000000)<sub>2</sub>.

Given: resolution = 22 mV, Input = (1000000)<sub>2</sub>

Resolution =

$$\frac{V_{oFS}}{2^n - 1}$$

$$\frac{V_{oFS}}{2^8-1}$$

as large galaxs as another 1  $\sim$  2  $\frac{V_{oFS}}{2^8-1}$  as the property of the property of

$$\epsilon_{\rm opt}$$

of recovery = 5.6 V recovery lateral and the supple and the supple supple supplementary that the supplementary is the supplementary of the supp

$$D = \text{equivalent of } (10000000)_2 = 128$$

$$V_o = 22 \times 10^{-3} \times 128 = 2.8 \text{ V}.$$

#### Example 3:

Calculate output voltage produced by DAC, when output range is between 0 10 V for input binary number.

- a) 10 (2 bit DAC) b) 0011

- From equation (9-7) we can write, a)

$$V_o = 10 \text{ V} \left( 1 \times \frac{1}{2} + 0 \times \frac{1}{4} \right) = 5 \text{ V}$$

From equation (9-7) we can write, b)

$$V_o = 10 \text{ V} \left( 0 \times \frac{1}{2} + 0 \times \frac{1}{4} + 1 \times \frac{1}{8} + 1 \times \frac{1}{16} \right)$$

= 1.875 volts.

#### Example 4:

Calculate the values of the LSB and full scale output for 4 bit DAC for 0 to 10 V range.

We have,

LSB =

$$\frac{1}{2^4} = \frac{1}{16}$$

For 10 V range,

LSB =

$$\frac{10 \text{ V}}{16}$$

= 625 mV

and

$$MSB = \left(\frac{1}{2}\right) Fullscale$$

$$= \frac{1}{2} \times 10 = 5 V$$

Full scale output = Full scale voltage -1 LSB

$$= 10 - 625 \text{ mV} = 9.375 \text{ V}$$

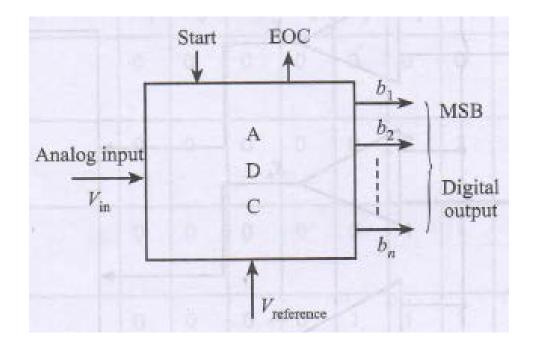

### **A-D Converters**

Types: Direct type ADCs and Integrated type ADCs

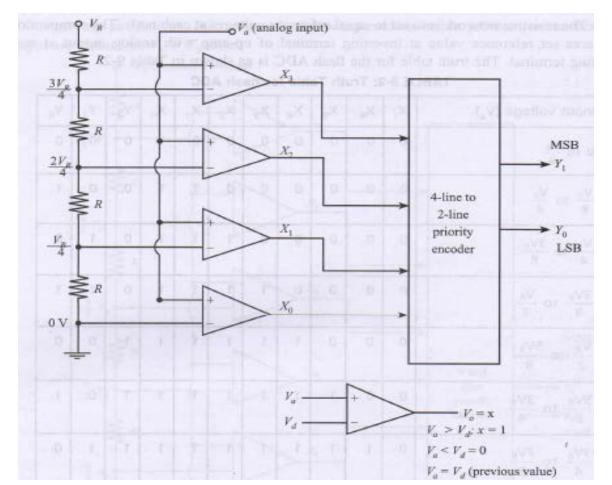

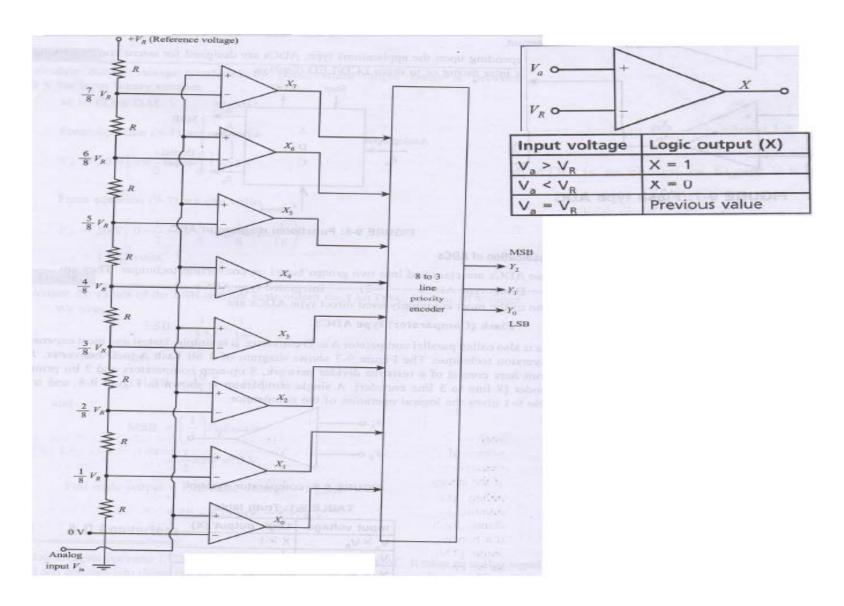

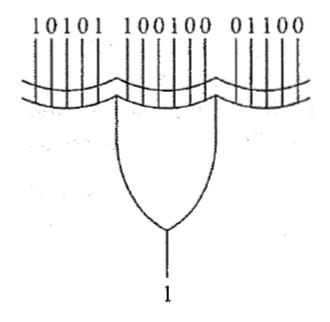

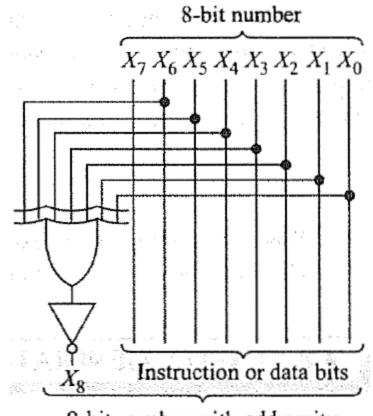

# Flash (Comparator/ Parallel) type ADC:

# Flash (Comparator/ Parallel) type ADC:

| Analog input voltage (V <sub>a</sub> ) | X <sub>3</sub> | X <sub>2</sub> | X <sub>1</sub> | X <sub>0</sub> | Y <sub>1</sub> | Yo |

|----------------------------------------|----------------|----------------|----------------|----------------|----------------|----|

| 0 to $\frac{V_R}{4}$                   | 0              | 0              | 0              | 1              | 0              | 0  |

| $\frac{V_R}{4}$ to $\frac{2V_R}{4}$    | 0              | 0              | 1              | 1              | 0              | 1  |

| $\frac{2V_R}{4}$ to $\frac{3V_R}{4}$   | 0              | 1              | 1              | 1              | 1              | 0  |

| $\frac{3V_R}{4}$ to $V_R$              | 1              | 1              | 1              | 1              | 1              | 1  |

| Input voltage (V <sub>s</sub> )        | X, | X <sub>6</sub> | X <sub>5</sub> | X <sub>4</sub> | X <sub>3</sub> | X <sub>2</sub> | X <sub>1</sub> | X <sub>o</sub> | Y <sub>2</sub> | Y | Y <sub>0</sub> |

|----------------------------------------|----|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|---|----------------|

| 0 to V <sub>R</sub>                    | 0  | 0              | 0              | 0              | 0              | 0              | 0              | 1              | 0              | 0 | 0              |

| V <sub>R</sub> to V <sub>R</sub>       | 0  | 0              | 0              | 0              | 0              | 0              | 1              | 1              | 0              | 0 | 1              |

| $\frac{V_R}{4}$ to $\frac{3V_R}{8}$    | 0  | 0              | 0              | 0              | 0              | 1              | 1              | 1              | 0              | 1 | 0              |

| $\frac{3V_R}{8}$ to $\frac{V_R}{2}$    | 0  | 0              | 0              | 0              | 1              | 1              | 1              | 1              | 0              | 1 | 1              |

| $\frac{V_R}{2}$ to $\frac{5V_R}{8}$    | 0  | 0              | 0              | 1              | 1              | 1              | 1              | 1              | 1              | 0 | 0              |

| $\frac{5V_R}{8}$ to $\frac{3V_R}{4}$   | 0  | 0              | 1              | 1              | 1              | 1              | 1              | 1              | 1              | 0 | 1              |

| $\frac{3V_R^1}{4}$ to $\frac{7V_R}{8}$ | 0  | 1              | 1              | 1              | 1              | 1              | 1              | 1              | 1              | 1 | 0              |

| 7V <sub>R</sub> to V <sub>R</sub>      | 1  | 1 10           | 1              | 4              | 1              | 1              | do             | 1              | 1              | 1 | 1              |

# Flash (Comparator/ Parallel) type ADC:

- Advantages:

- High speed

#### Disadvantages:

- Number of comparators required is almost double for each added bit

- Eg.: For 2-bit ADC; No. of Comparators = 4 (22)

For 3-bit ADC; No. of Comparators = 8 (23)

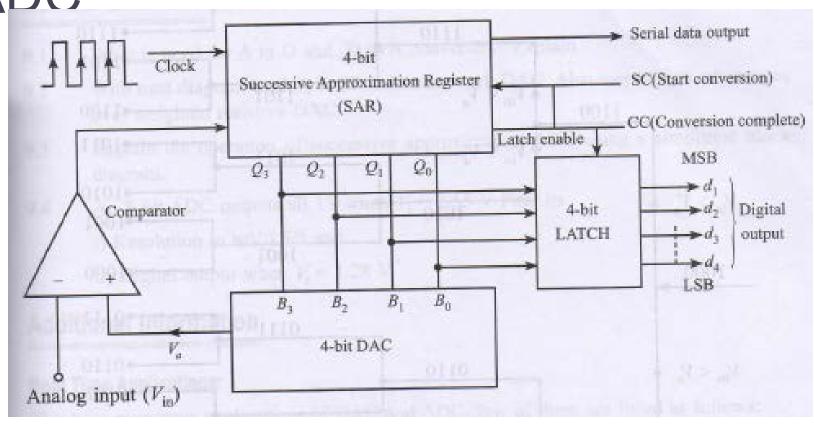

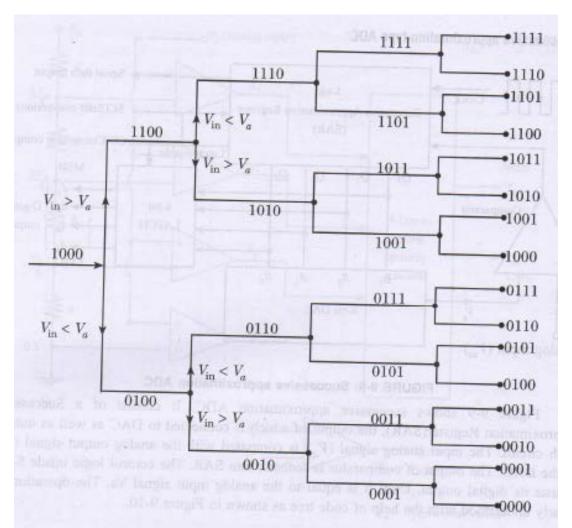

Successive Approximation type ADC

# Successive Approximation type ADC

# Successive Approximation type ADC

- The conversion time for n-bit successive approximation ADC is (n + 2) clock periods.

- Advantages:

- Considerably good speed

- Good resolution.

# Module-2

11

The Basic Gates & Combinational Logic Circuits

#### **Text Books Referred**

Donald P Leach, Albert Paul Malvino & Goutam Saha: Digital Principles and Applications, 7<sup>th</sup> Edition, Tata McGraw Hill, 2015

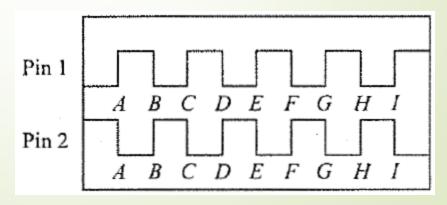

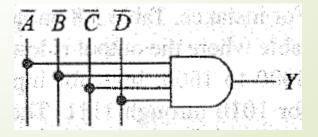

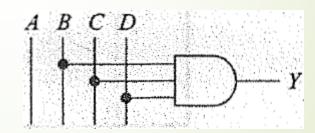

- A logic gate is a digital circuit with 1 or more input voltages but only 1 output voltage.

- Logic gates are the fundamental building blocks of digital systems.

- By connecting the different gates in different ways, we can build circuits that perform arithmetic and other functions associated with the human brain.

- Because the circuits simulate mental processes, gates are often called logic circuits. NOT, OR & AND gates are the basic types of gates.

- The inter-connection of gates to perform a variety of logical operations is called logic design.

- The operation of a logic gate can be easily understood with the help of "truth table".

- A truth table lists all possible combinations of inputs and the corresponding outputs.

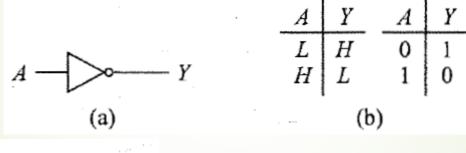

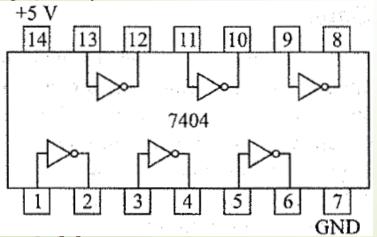

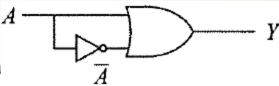

- **NOT GATE (INVERTER)**

- It is a gate with only 1 input and a complemented output.

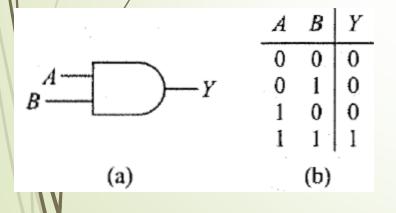

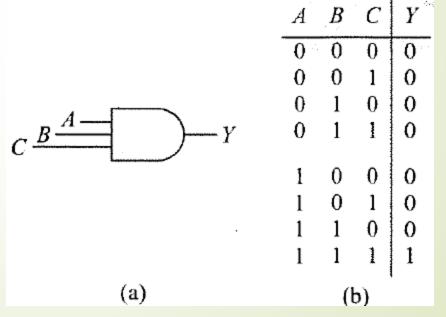

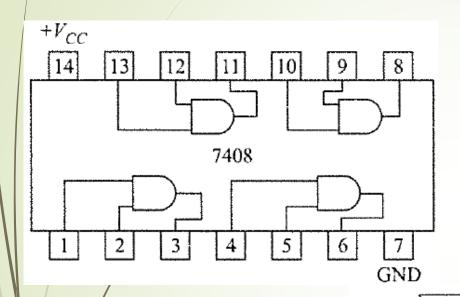

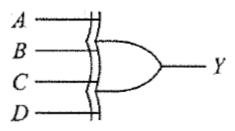

- AND GATE

- This is a gate with 2 or more inputs.

- The output is HIGH only when all inputs are HIGH.

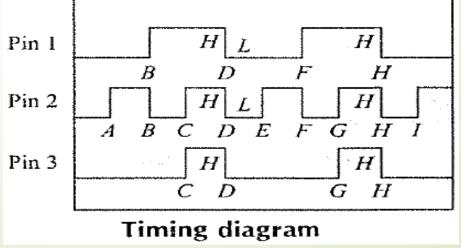

- **OR GATE**

- This is a gate with 2 or more inputs.

- The output is HIGH when any input is HIGH.

|                                       | $\boldsymbol{A}$ | B   | Ç  | Y             |

|---------------------------------------|------------------|-----|----|---------------|

|                                       | 0                | 0   | 0  | 0             |

|                                       | 0                | 0   | 1  | 1             |

|                                       | ()               | 1   | 0  | 1             |

| $B \xrightarrow{A} Y$                 | 0                | 1   | 1  | 1             |

| $C = \bigcup_{i \in \mathcal{I}} C_i$ |                  | ٠.  |    |               |

|                                       | 1                | . 0 | 0  | 1             |

| and the same of the same              | 1                | 0   | 1  | 1             |

|                                       | 1                | 1   | 0  | 1             |

|                                       | 1                | 1   | 1  | 1             |

| (a)                                   | . 42%            | (   | b) | nesse<br>Disk |

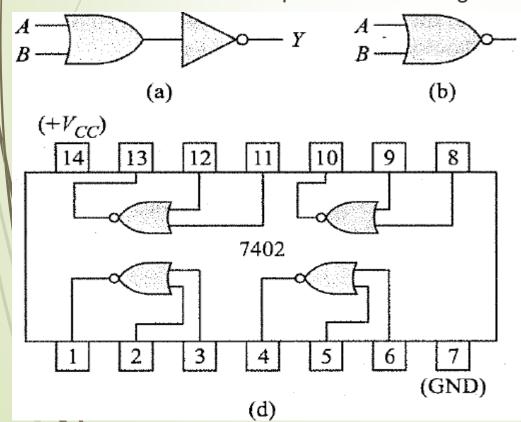

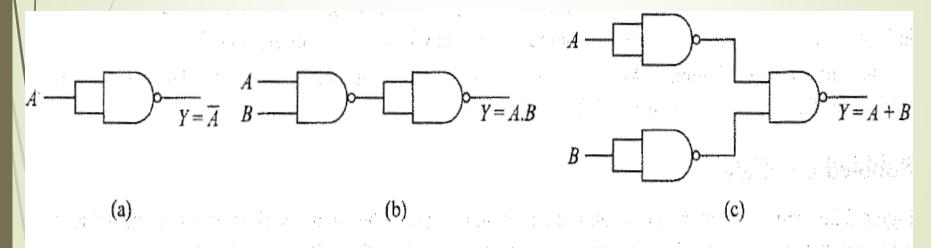

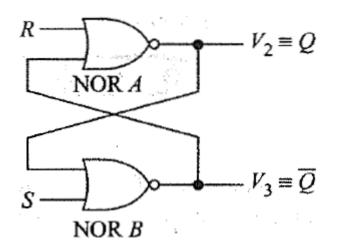

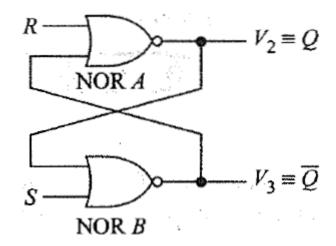

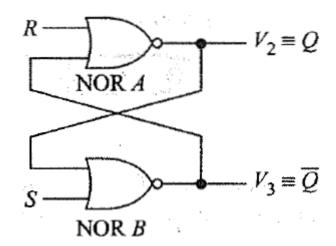

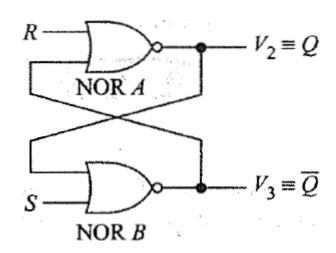

#### **NOR GATE**

This represents an OR gate followed by an inverter.

| 4 | В | ¥ |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

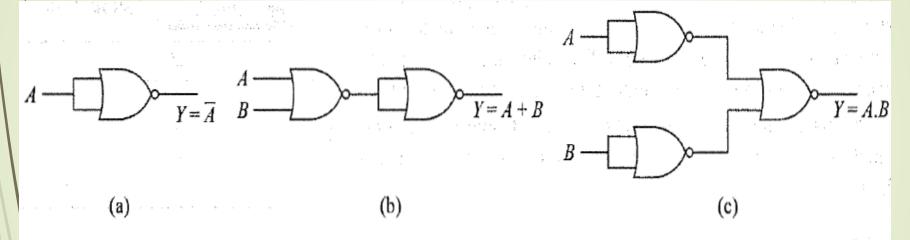

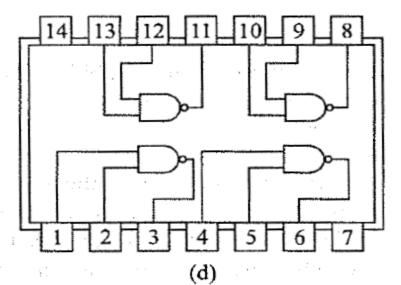

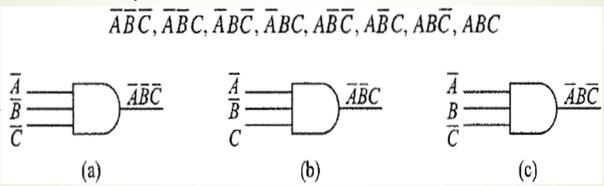

Universality of NOR gate (a) NOT from NOR, (b) OR from NOR, (c) AND from NOR

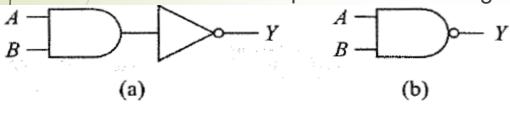

#### **NAND GATE**

This represents an AND gate followed by an inverter.

| A | В |     | Y     |

|---|---|-----|-------|

| 0 | 0 |     |       |

| 0 | 1 |     |       |

| 1 | 0 |     | 1,000 |

| 1 | 1 | , , | 0     |

Universality of NAND Gate

Universality of NAND gate: (a) NOT from NAND, (b) AND from NAND, (c) OR from NAND

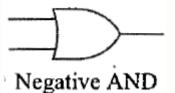

- We use a binary 0 for low voltage and a binary 1 for high voltage. This is called positive logic.

- Another code known as negative logic where binary 0 stands for high voltage and binary 1 for low voltage.

- Positive and Negative Gates

- An OR gate in a positive logic system becomes an AND gate in a nega Positive OR n.

| . A | Υ |

|-----|---|

| 0 0 | 0 |

| 0 1 | 1 |

| i 0 | 1 |

| 1   | 1 |

| <b>A</b> 100000 | . : <i>B</i> | <b>Y</b> |

|-----------------|--------------|----------|

| 1 1             | 1            | 12       |

| 1               | 0            | 0        |

| 0               | I            | 0        |

| 0               | 0            | 0        |

Positive logic system

**Negative logic system**

In a similar way, we can show the truth table of other gates with positive or negative logic. By analysing the inputs and outputs in terms of 0s and ls, you find these equivalences between the positive and negative logic:

Positive OR

→ negative AND

Positive AND

→ negative OR

Positive NOR

→ negative NAND

Positive NAND

→ negative NOR

| Gate                       | Definition                               |

|----------------------------|------------------------------------------|

| Positive OR/negative AND   | Output is high if any input is high.     |

| Positive AND/negative OR   | Output is high when all inputs are high. |

| Positive NOR/negative NAND | Output is low if any input is high.      |

| Positive NAND/negative NOR | Output is low when all inputs are high.  |

- Assertion-level logic

- Logic circuits with bubbles on all pins with active-low signals and omit bubbles on all pins with active-high signals. This use of bubbles with active-low signals is called assertion-level logic.

- If a low input signal turns on a chip, you show a bubble on that input. If a low output is a sign of chip action, you draw a bubble on that output. Once you get used to assertion-level logic, you may prefer drawing logic circuits this way.

- DL is a language that describes the hardware of digital systems in a textual form. It resembles a programming language, but is specifically oriented to describing hardware structures, dataflow and behaviors.

- The main difference with the traditional programming languages is HDL's representation of extensive parallel operations whereas traditional ones represents mostly serial operations. HDL can be used to represent logic diagrams, Boolean expressions, and other more complex digital circuits

- There are two standard HDL's that are supported by IEEE.

- VHDL (Very-High-Speed Integrated Circuits Hardware Description Language) - Sometimes referred to as VHSIC HDL, this was developed from an initiative by US. Dept. of Defense.

- Verilog HDL developed by Cadence Data systems and later transferred to a consortium called Open Verilog International (OVI).

- Verilog: Verilog HDL has a syntax that describes precisely the legal constructs that can be used in the language.

- It uses about 100 keywords pre-defined, lowercase, identifiers that define the language constructs.

- Example of keywords: module, endmodule, input, output wire, and, or, not, etc.,

- Any text between two slashes (//) and the end of line is interpreted as a comment.

- Blank spaces are ignored and names are case sensitive.

- A module is the building block in Verilog. It is declared by the keyword module and is always terminated by the keyword endmodule. Each statement is terminated with a semicolon, but there is no semi-colon after endmodule.

```

module or_gate (A, B, Y);

input A, B; // defines two input port

output Y; // defines one output port

or g1(Y,A,B); /*Gate declaration with predefined

keyword or representing logic OR, g1 is optional

user defined gate indentifier*/

endmodule

```

- The syntax for the basic gate

- E.g. For OR gate or (output, input 1, input 2, input 3, input 4)

- For NOT gate, not (output, input)

endmodule

```

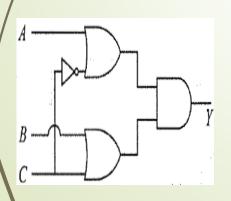

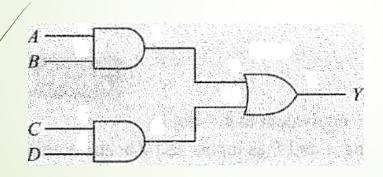

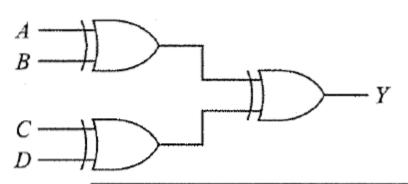

module eg1(A,B,C,D,Y);

input A,B,C,D;

output Y;

wire and_opl, and_op2;

and gl(and_opl,A,B); //g1 represents upper AND gate

and g2(and_op2,C,D); //g2 represents lower AND gate

or g3(Y,and_opl,and_op2); // g3 represents the OR gate

```

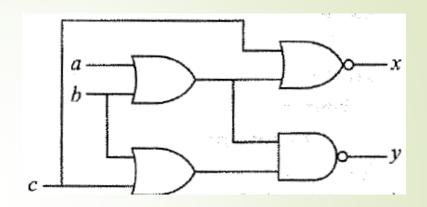

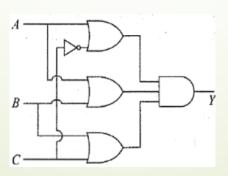

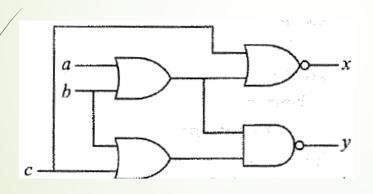

```

module eg2(a,b,c,x,y);

input a,b,c;

output x,y;

wire or_op1, or_op2;

or g1(or_op1,a,b);

or g2(or_op2,b,c);

nor g13(x,c,or_op1);

nand g4(y,or_op1,or_op2);

endmodule

```

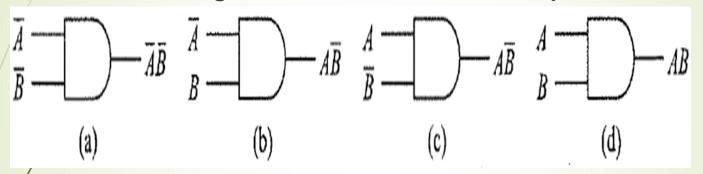

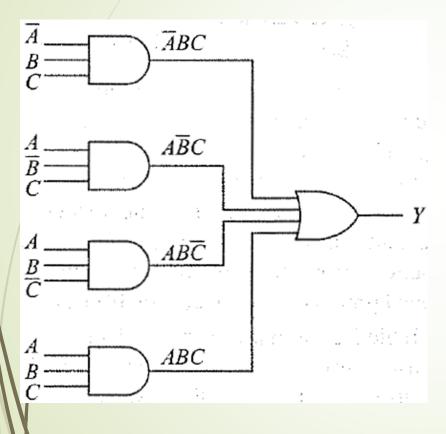

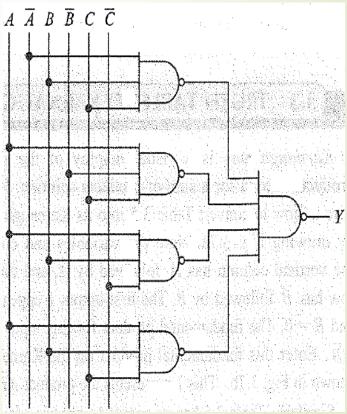

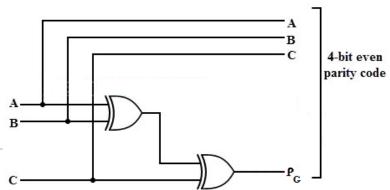

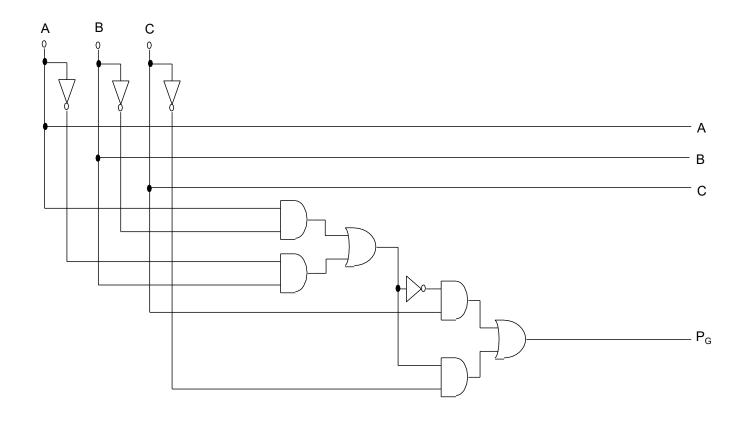

- Possible ways to AND two or more input signals that are in complement and un-complement form.

- A SOP expression is two or more AND functions ORed together.

ANDing two variables and their complements

| -A | В | Fundamental Product        |  |

|----|---|----------------------------|--|

| 0  | 0 | $\overline{A}\overline{B}$ |  |

| 0  | 1 | $\overline{A}B$            |  |

| 1  | 0 | $A\overline{B}$            |  |

| 1  | 1 | AB                         |  |

- The fundamental products are also called minterms.

- Products  $\overline{AB}$ ,  $\overline{AB}$ ,  $\overline{AB}$ ,  $\overline{AB}$ ,  $\overline{AB}$ ,  $\overline{AB}$  are represented by m0, m1, m2 and m3 respectively. The suffix i of mi comes from decimal equivalent of binary values that makes corresponding product term high.

#### Example:

| $A_{++}$ | В | , C | Fundamental Products        |

|----------|---|-----|-----------------------------|

| 0        | 0 | 0   | $\overline{ABC}$            |

| 0        | 0 | 1   | $\overline{ABC}$            |

| 0        | 1 | 0   | $\overline{A}B\overline{C}$ |

| 0        | 1 | 1   | $\overline{A}BC$            |

| 1        | 0 | 0   | $A\overline{B}\overline{C}$ |

| 1        | 0 | 1   | $A\overline{B}C$            |

| 1        | 1 | 0   | $AB\overline{C}$            |

| 1        | 1 | 1   | ABC                         |

- ♦ The above three variable minterms can alternatively be represented by mo, m1, m2, m3, m4, m5, m6, and m7 respectively. Note that, for n variable problem there can be 2<sup>n</sup> number of minterms.

- ♦ The fundamental products by listing each one next to the input condition that results in a high output.

- ❖ For instance, when A = 1, B = 0 and C = 0, the fundamental product results in an output of

$$Y = A\overline{B}\overline{C} = 1 \cdot \overline{0} \cdot \overline{0} = 1$$

## **Sum-of-Products Equation-1**

- Sum-of-Products Equation

- The Sum-of-products solution, for given a truth table shown below.

| A | В | c             | ·Y  |

|---|---|---------------|-----|

| 0 | 0 | 0             | . 0 |

|   | 0 | outer 1 Trans | 0   |

| 0 | 1 | 0             | O   |

| 0 | 1 | 1             | 1   |

| 1 | 0 | 0             | 0   |

| 1 | 0 | 1             | 1   |

| 1 | 1 | 0             | 1   |

| 1 | 1 | i I           | 1   |

Write down the fundamental product for each output 1 in the truth table. For example, the first output 1 appears for an input of A = 0, B = 1, and C = 1. The corresponding fundamental product is ABC.

## **Sum-of-Products Equation-2**

| alen den de se | B  | e e e e e e e e e e e e e e e e e e e | Y                              |

|----------------|----|---------------------------------------|--------------------------------|

| 0              | .0 | 0                                     | 0                              |

| 0 2534         | 0  | nadal <b>l</b> ood k                  | 0                              |

| 0              | 1  | 0                                     | 0                              |

| 0 3            | 1  | 1                                     | $1 \rightarrow \overline{A}BC$ |

| 1              | 0  | 0                                     | 0                              |

|                | 0  | 1                                     | $1 \rightarrow A\overline{B}C$ |

| 1              | 1  | 0                                     | $1 \rightarrow AB\overline{C}$ |

| 1              | 1  | 1                                     | $1 \rightarrow ABC$            |

To get the sum-of-products equation, all you have to do is OR the fundamental products

$$Y = \overline{A}BC + A\overline{B}C + AB\overline{C} + ABC$$

Alternate representation

$$Y = F(A, B, C) = \sum m(3, 5, 6, 7)$$

## **Sum-of-Products Equation-3**

♦ where '∑:' symbolizes summation or logical OR operation that is performed on corresponding minterm's and Y = F (A, B, C) means Y is a function of three Boolean variables A, B and C. This kind of representation of a truth table is also known as canonical sum form.

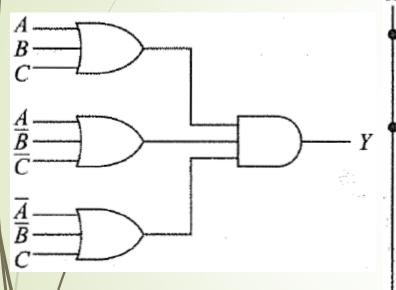

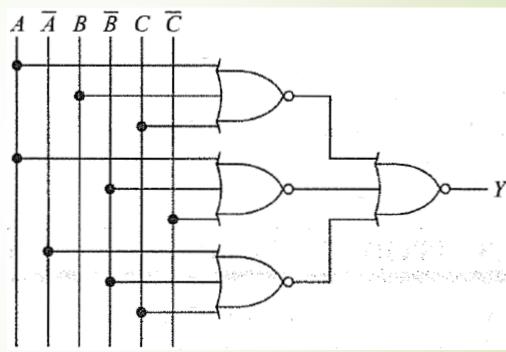

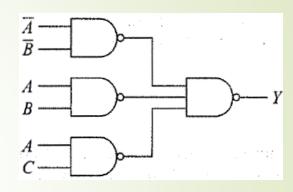

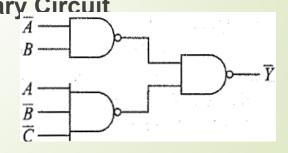

# **Logic Circuit**

## **Logic Circuit**

#### Lab Experiment

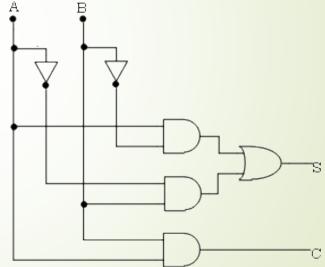

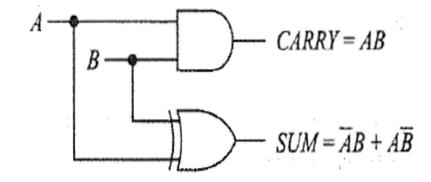

- Design and implement Half adder, Full Adder, Half Subtractor, Full Subtractor using basic gates.

- Half Adder:

- Truth Table for Half Adder <sup>A</sup> •

|   | Input |     | Oı      | utput            |

|---|-------|-----|---------|------------------|

|   | A     | В   | Sum (S) | Carry (C)        |

| 1 | 0     | 0 / | 0       | 0                |

|   | 0     | 1/  | 1       | 0                |

|   | 1     | 0   | 1       | 0                |

|   | 1     | / 1 | 0       | Logic Expression |

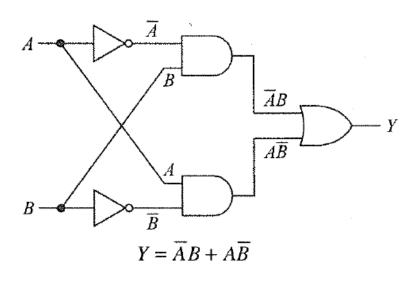

- $ightharpoonup S = \overline{A}.B + A.\overline{B}$

- C = A. B

## **Logic Circuit**

#### Laws and Rules of Boolean Algebra

Commutative Law

Associative Law

Distributive Law

**Null Elements**

Identity

Idempotence

Complement

Involution

Absorption (Covering)

Simplification

DeMorgan's Rule

Logic Adjacency (Combining)

Consensus

$$A+B=B+A$$

$$A + (B + C) = (A + B) + C$$

$$A \cdot (B+C) = A \cdot C + A \cdot B$$

$$A+1=1$$

$$A+0=A$$

$$A + A = A$$

$$A + \bar{A} = 1$$

$$\bar{\bar{A}} = A$$

$$A + A \cdot B = A$$

$$A + \bar{A} \cdot B = A + B$$

$$\overline{A+B} = \overline{A} \cdot \overline{B}$$

$$A \cdot B + A \cdot \bar{B} = A$$

$$A \cdot B + B \cdot C + \bar{A} \cdot C = A \cdot B + \bar{A} \cdot C$$

$$A \cdot B = B \cdot A$$

$$A \cdot (B \cdot C) = (A \cdot B) \cdot C$$

$$A+B\cdot C=(A+B)\cdot (A+C)$$

$$A \cdot 0 = 0$$

$$A \cdot 1 = A$$

$$A \cdot A = A$$

$$A \cdot \bar{A} = 0$$

$$A \cdot (A + B) = A$$

$$A \cdot (\bar{A} + B) = A \cdot B$$

$$\overline{A \cdot B} = \overline{A} + \overline{B}$$

$$(A+B)\cdot (A+\bar{B})=A$$

$$(A+B)\cdot (B+C)\cdot (\bar{A}+C)=$$

$$(A+B)\cdot(\bar{A}+C)$$

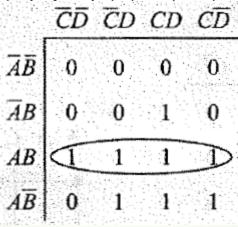

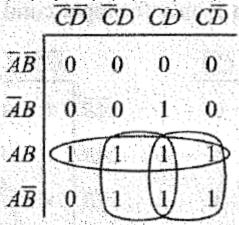

# TRUTH TABLE TO KARNAUGH MAP-1

- A Karnaugh map (K-Map) is a visual display of the fundamental products needed for a sum-of-products solution.

- Also simplification of logical expression.

# TRUTH TABLE TO KARNAUGH MAP-2

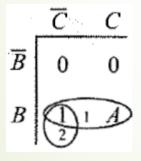

#### ♦ Two-Variable Maps

Examp

| r | A   | В | Y |

|---|-----|---|---|

| ۲ | 0   | 0 | 0 |

|   | 0   | 1 | 0 |

|   | Î . | 0 | 1 |

|   | 1   | 1 | 1 |

|                            | $\widetilde{B}$ | В |

|----------------------------|-----------------|---|

| $\overline{\widetilde{A}}$ |                 |   |

| A                          |                 |   |

| $\overline{B}$ |   | В |

|----------------|---|---|

| $\overline{A}$ | 0 | 1 |

| A              | 2 | 3 |

| _              | $\overline{B}$ | B |

|----------------|----------------|---|

| $\overline{A}$ |                |   |

| A              | 1              |   |

|                  | $\overline{B}$ | B |

|------------------|----------------|---|

| $\overline{A}$   |                |   |

| $\boldsymbol{A}$ | 1              | 1 |

| $\overline{B}$ |   | В |

|----------------|---|---|

| $\overline{A}$ | 0 | 0 |

| A              | 1 | 1 |

$\diamondsuit$  Example Y = F(A B)= $\Sigma$ m(1 2 3)

| Α | В        | Y             |

|---|----------|---------------|

| 0 | 0        | 0             |

| 0 | 1        | 1             |

| 1 | 0        | 1 <del></del> |

| 1 | 1        | 1             |

| 7 | Couth Ta | ı<br>able     |

|   | 111 / | ו כ. |   |

|---|-------|------|---|

| B | 0     | 1    |   |

| 0 | 0     | 1    | - |

| 1 | 1     | 1    |   |

| Y |       |      |   |

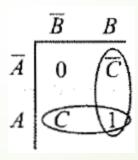

**♦ Three-Variable Maps**

$\Leftrightarrow$  Example: Y = F(A, B, C) =  $\sum m(2.6.7)$

| 1 m(2 6 7 | B | C | Y   |

|-----------|---|---|-----|

| 0         | 0 | 0 | 0   |

| 0         | 0 | 1 | 0 . |

| 0         | 1 | 0 | 1   |

| 0         | 1 | 1 | 0   |

| 1         | 0 | 0 | 0   |

| 1         | 0 | 1 | 0   |

|           | 1 | 0 | 1   |

| 1         | 1 | 1 | 1   |

|                            | $\overline{C}$ | С |

|----------------------------|----------------|---|----------------------------|----------------|---|----------------------------|----------------|---|----------------------------|----------------|---|

| $\overline{A}\overline{B}$ |                |   | $\overline{A}\overline{B}$ | 0              | 1 | $\overline{A}\overline{B}$ |                |   | $\overline{A}\overline{B}$ | 0              | 0 |

| $\overline{A}B$            |                |   | $\overline{A}B$            | 2              | 3 | $\overline{A}B$            | 1              |   | $\overline{A}B$            | 1              | 0 |

| AB                         |                |   | · AB                       | 6              | 7 | AB.                        | 1              | 1 | AB                         | 1              | 1 |

| $A\overline{B}$            |                |   | $A\overline{B}$            | 4              | 5 | $A\overline{B}$            |                |   | $A\overline{B}$            | 0              | 0 |

14 6

### TRUTH TABLE TO KARNAUGH MAP-4

$\overline{AB}$ ,  $\overline{AB}$ ,  $\overline{AB}$ ,  $\overline{AB}$ ?

|                            | $\overline{C}$ | C |                            | Ĉ          | C |

|----------------------------|----------------|---|----------------------------|------------|---|

| $\overline{A}\overline{B}$ |                |   | $\overline{A}\overline{B}$ | 0          | 1 |

| $\overline{A}B$            |                |   | $\overline{A}B$            | 2          | 3 |

| AB                         | . :            |   | · AB                       | 6          | 7 |

| $A\overline{B}$            |                |   | $A\overline{B}$            | 4          | 5 |

|                            | (a)            |   |                            | <u>(</u> t | ) |

|                             | <del>C</del> | С |

|-----------------------------|--------------|---|

| $\overline{A}\widetilde{B}$ | 0            | 1 |

| $\overline{A}B$             | 2            | 3 |

| AB                          | 6            | 7 |

| $A\overline{B}$             | 4            | 5 |

|                             | (b           | ) |

$\overline{AB}$ ,  $\overline{AB}$ ,  $\overline{AB}$ ,  $\overline{AB}$ ?

|                            | $\overline{C}$ $C$ |                            | Ĉ  | C |

|----------------------------|--------------------|----------------------------|----|---|

| $\overline{A}\overline{B}$ |                    | $\overline{A}\overline{B}$ | 0  | 1 |

| $\overline{A}B$            |                    | $\overline{A}B$            | 2  | 3 |

| AB                         |                    | · AB                       | 6  | 7 |

| $A\overline{B}$            |                    | $A\overline{B}$            | 4  | 5 |

|                            | (a)                |                            | (t | ) |

|                            | C  | C |

|----------------------------|----|---|

| $\overline{A}\overline{B}$ | 0  | 1 |

| ĀВ                         | 2  | 3 |

| AB                         | 6  | 7 |

| $A\overline{B}$            | 4  | 5 |

| -                          | (t | ) |

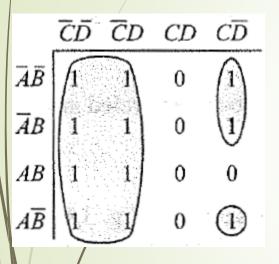

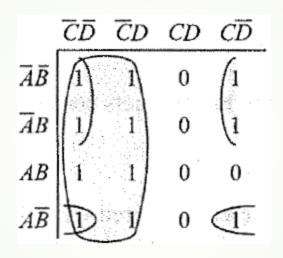

- ♦ Four-Variable Maps

- ♦ Example:  $Y = F(A,B,C,D) = \sum m(1,6,7,14)$

| 11010. 1 |       | 1,0,0,0               |    | 7 111( 1,0 |

|----------|-------|-----------------------|----|------------|

| A        | В     | C                     | D  | <i>Y</i>   |

| 0        | 0     | 0                     | 0  | 0          |

| 0        | 0     | 0                     | 1  | 1          |

| 0        | 0     | 1                     | 0  | 0          |

| 0        | 0     | 1                     | 1  | 0          |

| 0        | 1     | 0                     | 0  | 0<br>0     |

| 0        | 1     | 0                     | 1  | 0          |

| 0        | 1     | 1                     | 0  | 1          |

| 0        | 1     | 1                     | 1  |            |

| 1        | 0     | 0                     | 0  | 0          |

| 1        | 0     | 0                     | 1  | 0          |

| 1        | 0     | 1                     | 0  | 0          |

| 1        | 0     | 1                     | 1  | . 0        |

| 1        | 1     | 0                     | 0  | 0          |

| 1        | ì     | 0                     | 1  | . 0        |

| 1.       | 1     | $\cdot \cdot \cdot 1$ | 0  | <b>1</b>   |

| 1        | . The | 1                     | :1 | 0          |

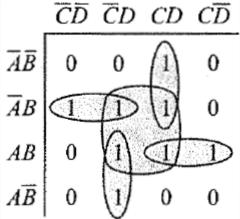

|                            | $\overline{C}\overline{D}$ | $\overline{C}D$ | CD | $C\overline{D}$ |                            | $\overline{C}\overline{D}$ | $\overline{C}D$ | CD   | $C\overline{D}$ |                            | $\overline{C}\overline{D}$ | $\overline{C}D$ | CD | $C\widetilde{D}$ |                            | ·CD | $\overline{C}D$ | CD | $C\overline{D}$ |

|----------------------------|----------------------------|-----------------|----|-----------------|----------------------------|----------------------------|-----------------|------|-----------------|----------------------------|----------------------------|-----------------|----|------------------|----------------------------|-----|-----------------|----|-----------------|

| $\overline{A}\overline{B}$ | ł                          |                 |    | · · · · · ·     | $\overline{A}\overline{B}$ | 0                          | 1               | 3    | 2               | $\overline{A}\overline{B}$ | 0                          | 1               | 3  | 2                | $\overline{A}\overline{B}$ | 0   | 1               | 0  | 0               |

| $\overline{A}B$            | ŧ                          |                 |    |                 | $\overline{A}B$            | 4                          | 5               | 7    | 6 .             | $\overline{A}B$            | 4                          | , ,5            | 7  | 6                | $\overline{A}B$            | 0   | 0               | 1  | . 1             |

| AB                         |                            |                 |    |                 | AB                         | 12                         | 13              | 15   | 14              | AB                         | 12                         | 13              | 15 | 14               | AB                         | 0   | 0               | 0  | 1               |

| $A\overline{B}$            |                            |                 |    |                 | $A\overline{B}$            | 8                          | 9               | - 11 | 10              | $A\overline{B}$            | 8                          | 9               | 11 | 10               | $A\overline{B}$            | 0   | 0               | 0  | 0               |

|                            |                            |                 |    |                 |                            |                            |                 |      |                 |                            |                            |                 |    |                  |                            |     |                 |    |                 |

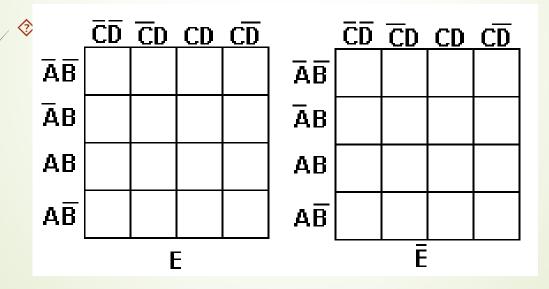

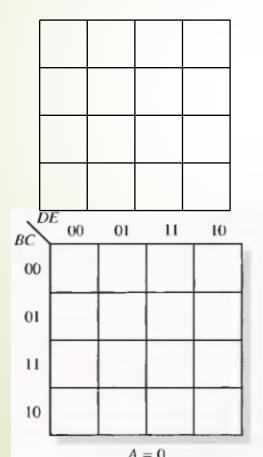

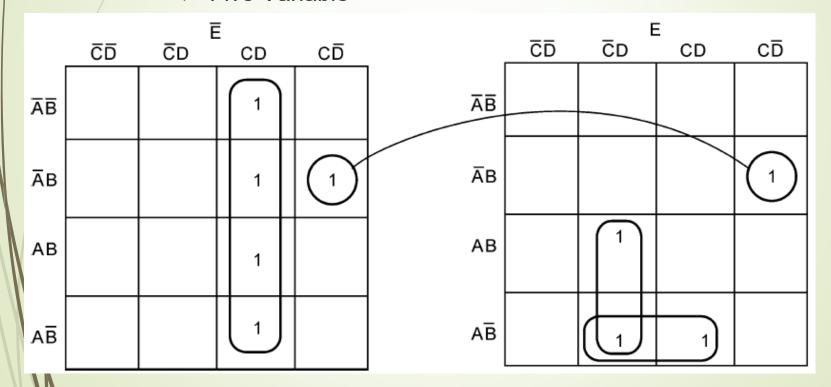

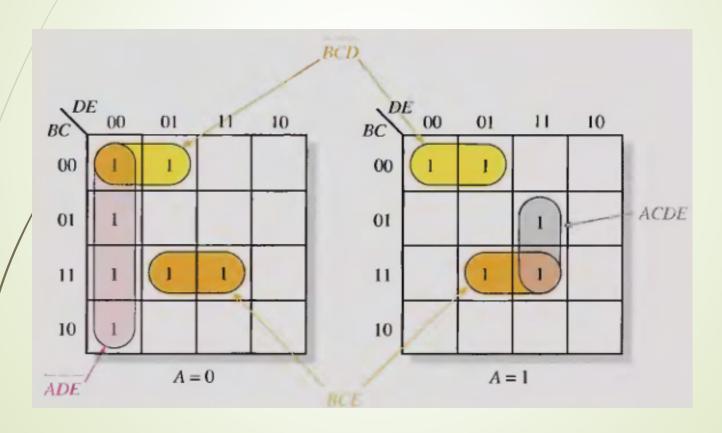

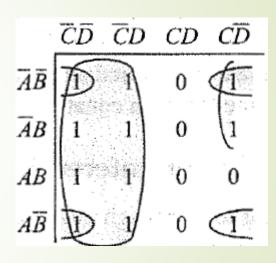

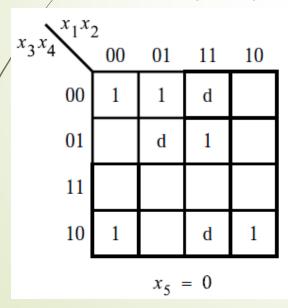

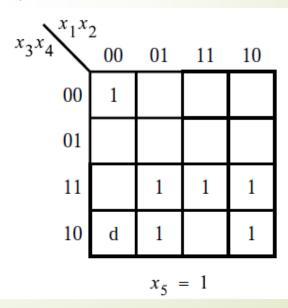

- ♦ Five-Variable Maps

- Example:

- ♦ Five-Variable Maps

- Example:

| <b>②</b> | ,                          | <u>CD</u> | <u>CD</u> | CD | CD |

|----------|----------------------------|-----------|-----------|----|----|

|          | $\overline{A}\overline{B}$ | 1         | 3         | 7  | 5  |

|          | ĀB                         | 9         | 11        | 15 | 13 |

|          | АВ                         | 25        | 27        | 31 | 29 |

|          | $A\overline{B}$            | 17        | 19        | 23 | 21 |

|          | •                          |           | F         | _  |    |

| ,  | <u>CD</u> | <u>C</u> D | CD | <u>CD</u> |  |  |  |  |

|----|-----------|------------|----|-----------|--|--|--|--|

| ĀB | 0         | 2          | 6  | 4         |  |  |  |  |

| ĀB | 8         | 10         | 14 | 12        |  |  |  |  |

| AB | 24        | 26         | 30 | 28        |  |  |  |  |

| ΑĒ | 16        | 18         | 22 | 20        |  |  |  |  |

| Ē  |           |            |    |           |  |  |  |  |

- ♦ Five-Variable Maps

- Example:

- ♦ Five-Variable Maps

- Example:

| <b>②</b> | ı                                 | ĒΒ | <u>CD</u> | CD | <u>CD</u> |

|----------|-----------------------------------|----|-----------|----|-----------|

|          | $\overline{A}\overline{B}$        | 1  | 0         | 1  | 0         |

|          | ĀΒ                                | 0  | 0         | 0  | 0         |

|          | AB                                | 1  | 0         | 1  | 0         |

|          | $\mathbf{A}\overline{\mathbf{B}}$ | 0  | 0         | 0  | 0         |

|          | !                                 |    | F         |    |           |

| ·               | <u>Ē</u> | <u>C</u> D | CD | <u>CD</u> |  |  |  |  |  |

|-----------------|----------|------------|----|-----------|--|--|--|--|--|

| ĀB              | 0        | 0          | 1  | 0         |  |  |  |  |  |

| ĀB              | 0        | 0          | 1  | 0         |  |  |  |  |  |

| AB              | 0        | 0          | 1  | 0         |  |  |  |  |  |

| $A\overline{B}$ | 0        | 0          | 0  | 1         |  |  |  |  |  |

| Ē               |          |            |    |           |  |  |  |  |  |

♦ Five-Variable Maps

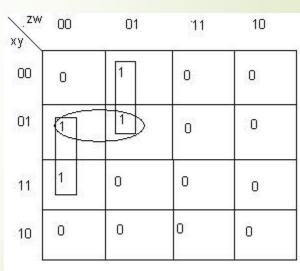

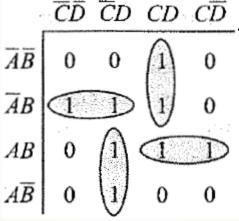

### PAIRS, QUADS, AND OCTETS-1

#### Pairs

The map contains a pair of 1s that are horizontally or vertically adjacent.

| / . · · · ·      | $\overline{C}\overline{D}$ | $\overline{C}D$ | CD | $C\overline{D}$ | 4.7 |                     | $\overline{C}\overline{D}$ | $\overline{C}D$ | CD | $C\overline{D}$ |

|------------------|----------------------------|-----------------|----|-----------------|-----|---------------------|----------------------------|-----------------|----|-----------------|

|                  |                            | 0               | 0  | 0               |     |                     |                            |                 | 0  |                 |

| $\overline{A}B$  | 1                          | 0               |    |                 |     | $\overline{A}B$     | 0                          | 0               | 0  | 0               |

| AB               | 0                          | 0               | 1  | 1               |     | AB                  | 0                          | 0.0             | (1 | 1)              |

| $A\widetilde{B}$ | 0                          | 0               | 0  | 0               |     | <br>$A\overline{B}$ | 0                          | 0               | 0  | 0               |

### PAIRS, QUADS, AND OCTETS-2

|                            | $\overline{C}\overline{D}$ | $\overline{C}D$ | CD | $C\overline{D}$ |                            | $\overline{C}\overline{D}$ | $\overline{C}D$ | CD  | $C\overline{D}$ |   | (              | $C\overline{D}$ | $\overline{C}D$ | CD | $C\overline{D}$ |                            | $\overline{C}\overline{D}$ | $\overline{CD}$ | CD    | $C\overline{D}$ |

|----------------------------|----------------------------|-----------------|----|-----------------|----------------------------|----------------------------|-----------------|-----|-----------------|---|----------------|-----------------|-----------------|----|-----------------|----------------------------|----------------------------|-----------------|-------|-----------------|

| $\overline{A}\overline{B}$ | 0                          | 0               | 0  | 0               | $\overline{A}\overline{B}$ | 0                          | 0               | (I) | 0               | Ã | $\bar{B}$      | 0               | 0               | 0  | 0               | $\overline{A}\overline{B}$ | 0                          | 0               | : / O | 0               |

| $\overline{A}B$            | 0                          | 0               | 0  | 0               | $\overline{A}B$            | 0                          | 0               |     | 0               | Ā | B              | 0               | 0               | 0  | 0               | $\overline{A}B$            | 0                          | 1               |       | 0               |

| AB                         | 0                          | 0               | 0  |                 | AB                         | Ö                          | 0               | 0   | 0               | A | iB             | 0               | 0               | 0  | 0               | AB                         | 1                          | 0               | 0     | 0               |

| $A\overline{B}$            | 0                          | 0,              | 0  | 1)              | $A\overline{B}$            | 0                          | 0               | 0   | 0               | A | $\overline{B}$ | 1               |                 | 0  | 0               | $A\overline{B}$            | 1                          | 0               | 0     | 0               |

### PAIRS, QUADS, AND OCTETS-3

- The Quad

- A quad is a group of four ls that are horizontally or vertically adjacent.

- A quad eliminates two variables and their complements.

|                            | $\overline{C}\overline{D}$ | $\overline{C}D$ | CD | $C\overline{D}$ |                 | $\overline{C}\overline{D}$ | $\overline{C}D$ | CD           | $C\overline{D}$ |   |                            | $\overline{C}\overline{D}$ | $\overline{C}D$ | CD | $C\overline{D}$ |

|----------------------------|----------------------------|-----------------|----|-----------------|-----------------|----------------------------|-----------------|--------------|-----------------|---|----------------------------|----------------------------|-----------------|----|-----------------|

| $\overline{A}\overline{B}$ | 0                          | 0               | 0  | 0               | $ar{A}ar{B}$    | 0                          | 0               | 0            | 0               |   | $\overline{A}\overline{B}$ | 0                          | 0               | 0  | 0               |

| $\overline{A}B$            | 0                          | 0               | 0  | 0               | $\overline{A}B$ | 0                          | 0               | 0            | 0               |   | $\overline{A}B$            | 0                          | 0               | 0  | 0               |

|                            |                            |                 |    |                 |                 |                            |                 | 1423 1522.23 | 1)              |   | AB                         | 1                          | 1)              | 1  | 1)              |

| $A\overline{B}$            | 0                          | 0               | 0  | 0               | $A\overline{B}$ | 0                          | 0               | 1            | 1)              | : | $A\overline{B}$            | 0                          | 0               | 0  | 0               |

### PAIRS, QUADS, AND OCTETS-4

- The Octet

- The octet is a group of eight 1 s.

- Octet eliminates three variables and their complements.

|                                                                 | ĈĎ      | $\overline{C}D$ | CD | $C\overline{D}$ |  |

|-----------------------------------------------------------------|---------|-----------------|----|-----------------|--|

| $\overline{A}\overline{B}$                                      | 0       | 0               | 0  | 0               |  |

| $\overline{A}B$                                                 | 0_      | 0               | 0  | 0               |  |

| $\overline{A}\overline{B}$ $\overline{A}B$ $AB$ $A\overline{B}$ | /1      | 1               | 1  | 1               |  |

| $A\overline{B}$                                                 | $ $ $ $ | 1               | 1  | 1)              |  |

|                                                                 | _       |                 |    |                 |  |

|                                        | $\overline{C}\overline{D}$ | $\overline{C}D$ | CD            | $C\overline{D}$ |

|----------------------------------------|----------------------------|-----------------|---------------|-----------------|

| $\overrightarrow{A}\overrightarrow{B}$ | 0                          | 0               | 0             | 0               |

| $\overline{A}B$                        | 0                          | 0               | 0             | 0               |

| AB                                     | 1                          | 1)              | $\int_{1}$    | 1               |

| $A\overline{B}$                        | $ \sqrt{1} $               | 1)              | $\bigcup_{1}$ | _1/             |

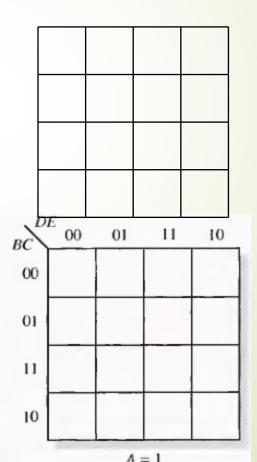

- SIMPLIFICATIONS-1

◆ The Karnaugh map uses the following rules for the simplification of expressions by *grouping* together adjacent cells containing *ones*.

- After drawing a Kamaugh map,

- Encircle the octets first,

- The quads second, and

- The pairs last.

|                            | $\overline{C}\overline{D}$ | $\overline{C}D$ | CD | $C\widetilde{D}$ | $\overline{C}\overline{D}$ $\overline{C}D$ $CD$ $C\overline{D}$   |

|----------------------------|----------------------------|-----------------|----|------------------|-------------------------------------------------------------------|

| $\overline{A}\overline{B}$ | 0                          | 1               | 1  | 1                | $\overline{A}\overline{B}$ 0 1                                    |

| $\overline{A}B$            | 0                          | 0               | 0  | 1                | $\overline{A}B$ 0 0 0 1                                           |

| AB                         | 1                          |                 | 0  | 1                | $AB \left( \begin{array}{c cc} 1 & 1 & 0 & 1 \end{array} \right)$ |

| $A\overline{B}$            | 1                          | 1               | 0  | 1                | $A\overline{B}$ $1$ $0$ $1$                                       |

$$Y = \overline{A}\overline{B}D + A\overline{C} + C\overline{D}$$

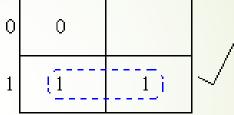

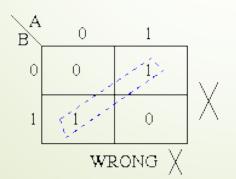

Groups may not include any cell containing a zero.

| 0 | ( <u>o</u> |  |

|---|------------|--|

| 1 |            |  |

WRONG X RIGHT √ **The State of the State of Sta**

16

#### KARNAUGH

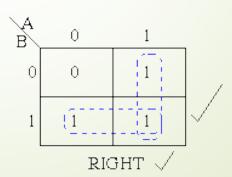

### SIMPLIFICATIONS-3 Groups must contain 1, 2, 4, 8, or in general 2<sup>n</sup> cells.

- That is if n = 1, a group will contain two 1's since  $2^1 = 2$ .

- $\Diamond$  If n = 2, a group will contain four 1's since  $2^2 = 4$ .

#### KARNAUGH

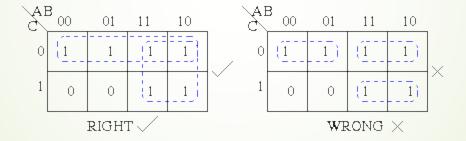

### SIMPLIFICATIONS-4 Each group should be as large as possible.

(Note that no Boolean laws broken, but not sufficiently minimal)

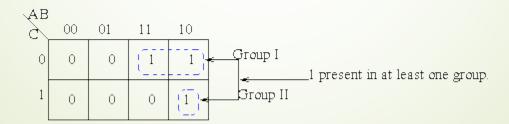

Each cell containing a one must be in at least one group.

16

#### KARNAUGH SIMPLIFICATIONS-5

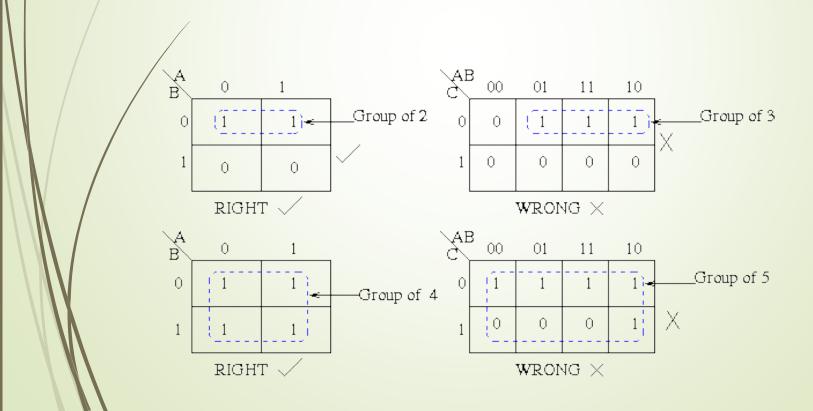

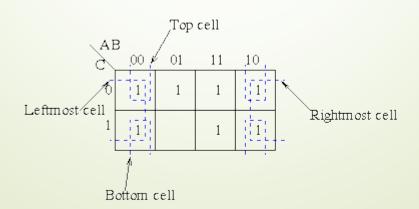

Groups may wrap (Rolling the Map) around the table. The leftmost cell in a row may be grouped with the rightmost cell and the top cell in a column may be grouped with the bottom cell.

| $\overline{A}\overline{B}$ 0 0 0 0 $\overline{A}\overline{B}$ 0 0 0 | 0          |

|---------------------------------------------------------------------|------------|

|                                                                     | U          |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$              | /i         |

| AB $1$ 0 0 $1$ $AB$ $1$ 0 0                                         | $\sqrt{1}$ |

| $A\overline{B} \mid 0  0  0  A\overline{B} \mid 0  0  0$            | 0          |

|                                                                     |            |

$$Y = B\overline{C}\overline{D} + BC\overline{D}$$

$$Y = B\overline{D}$$

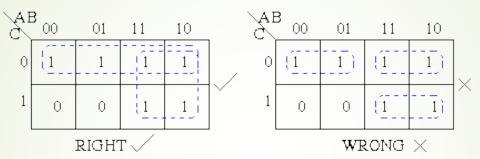

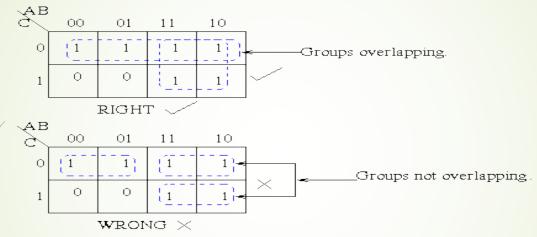

- Always overlap groups if possible

- Use the 1s more than once to get the largest groups you

|                  | $\overline{C}\overline{D}$ | $\overline{C}D$ | CD | $C\overline{D}$ |                            | $\overline{C}\overline{D}$ | $\overline{C}D$ | CD |

|------------------|----------------------------|-----------------|----|-----------------|----------------------------|----------------------------|-----------------|----|

| $\bar{A}\bar{B}$ | 0                          | 0               | 0  | 0               | $\overline{A}\overline{B}$ | 0                          | 0               | 0  |

| $\overline{A}B$  | 0                          | $\int \int$     | 0  | 0               | $\overline{A}B$            | 0                          | 1               | 0  |

| AB               | $\sqrt{1}$                 | W               | 1  | 1               | AB                         | $\sqrt{1}$                 | 1               | 1  |

| $A\overline{B}$  | 1                          | 1               | 1  | 1)              | $A\overline{B}$            | 1                          | 1               | 1  |

There should be as few groups as possible, as long as this does not contradict any of the previous rules.

Five Variable

$X = \overline{A}\overline{D}\overline{E} + \overline{B}\overline{C}\overline{D} + BCE + ACDE$

- No zeros allowed (Only in SOP).

- 2. No diagonals.

- 3. Only power of 2 number of cells in each group.

- 4. Groups should be as large as possible.

- 5. Every one must be in at least one group.

- 6. Overlapping allowed.

- Wrap around allowed.

- If possible roll and overlap to get the largest groups you can find.

- 9. Fewest number of groups possible.

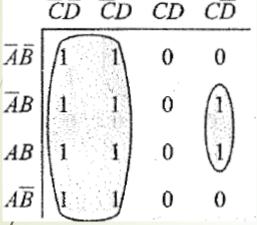

#### K- map grouping Examples-1

#### $\overline{C}\overline{D}$ $\overline{C}D$ $\overline{C}D$ CD $C\overline{D}$ and overlapping

$$Y = \overline{C} + BC\overline{D}$$

$$Y = \overline{C} + B\overline{D}$$

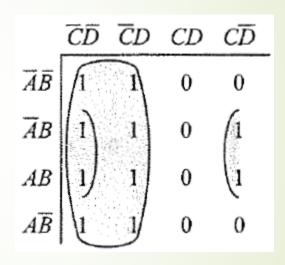

#### K- map grouping Examples-2

$$Y = \overline{C} + \overline{A}C\overline{D} + A\overline{B}C\overline{D}$$

$$Y = \overline{C} + \overline{A}\overline{D} + A\overline{B}\overline{D}$$

$$Y = \overline{C} + \overline{A}\overline{D} + \overline{B}\overline{D}$$

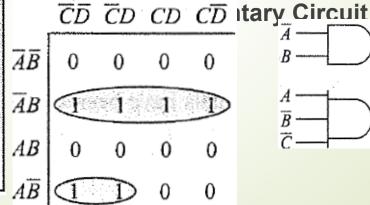

#### Eliminating Redundant

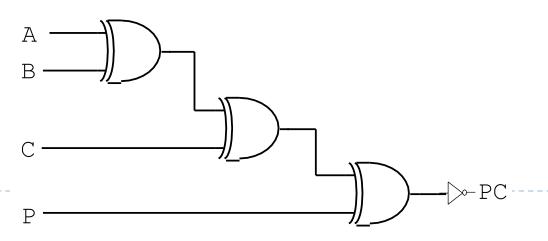

Groups-1